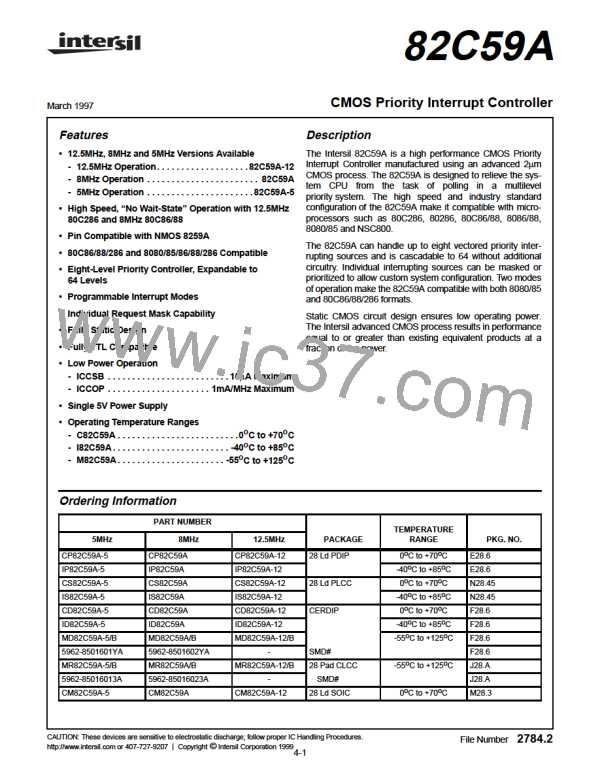

82C59A

o

o

o

o

AC Electrical Specifications

V

= +5.0V ±10%, GND = 0V, T = 0 C to +70 C (C82C59A), T -40 C to +85 C (l82C59A),

CC A A

o

o

T = -55 C to +125 C (M82C59A)

A

82C59A-5

82C59A

82C59A-12

TEST

SYMBOL

PARAMETER

MIN MAX MIN MAX MIN MAX UNITS CONDITIONS

TIMING REQUIREMENTS

(1) TAHRL

(2) TRHAX

(3) TRLRH

(4) TAHWL

(5) TWHAX

(6) TWLWH

(7) TDVWH

(8) TWHDX

(9) TJLJH

A0/CS Setup to RD/INTA

10

5

-

-

-

-

-

-

-

-

-

-

10

5

-

-

-

-

-

-

-

-

-

-

5

0

-

-

-

-

-

-

-

-

-

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

A0/CS Hold after RD/INTA

RD/lNTA Pulse Width

A0/CS Setup to WR

A0/CS Hold after WR

WR Pulse Width

235

0

160

0

60

0

5

5

0

165

240

5

95

160

5

60

70

0

Data Setup to WR

Data Hold after WR

Interrupt Request Width Low

100

55

100

40

40

30

(10) TCVlAL Cascade Setup to Second or Third INTA

(Slave Only)

(11) TRHRL

End of RD to next RD, End of INTA (within

an INTA sequence only)

160

-

160

-

90

-

ns

(12) TWHWL End of WR to next WR

190

500

-

-

190

400

-

-

60

90

-

-

ns

ns

(13) TCHCL

(Note 1)

End of Command to next command (not

same command type), End of INTA

sequence to next INTA sequence

TIMING RESPONSES

(14) TRLDV

(15) TRHDZ

(16) TJHlH

Data Valid from RD/INTA

-

5

-

160

100

350

565

-

5

-

120

85

-

5

-

40

22

90

50

ns

ns

ns

ns

1

2

1

1

Data Float after RD/INTA

Interrupt Output Delay

300

360

(17) TlALCV Cascade Valid from First INTA

(Master Only)

-

-

-

(18) TRLEL

Enable Active from RD or INTA

-

-

-

-

125

60

-

-

-

-

100

50

-

-

-

-

40

22

60

70

ns

ns

ns

ns

1

1

1

1

(19) TRHEH Enable Inactive from RD or INTA

(20) TAHDV

(21) TCVDV

Data Valid from Stable Address

Cascade Valid to Valid Data

210

300

200

200

NOTE:

1. Worst case timing for TCHCL in an actual microprocessor system is typically greater than the values specified for the 82C59A,

(i.e. 8085A = 1.6µs, 8085A -2 = 1µs, 80C86 = 1µs, 80C286 -10 = 131ns, 80C286 -12 = 98ns).

4-16

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]