TLE 6244X

1. Description

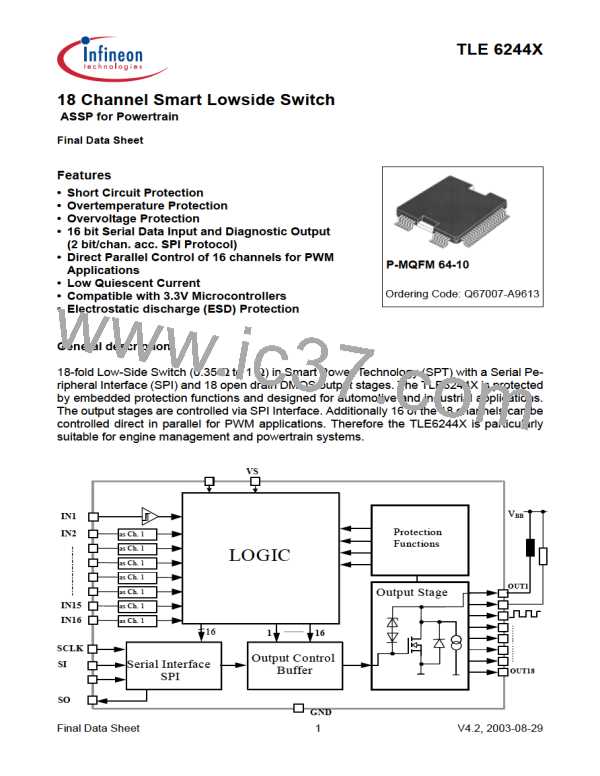

1.1 Short Description

This circuit is available in MQFP64 package or as chip.

1.1.1 Features of the Power Stages

Nominal Current

static current limita- Clamping

R

on,max at TJ = 25°C

tion enabled by SPI

2.2A

2.2A

1.1A

2.2A

2.2A

3.0A

1.1A

400mΩ

380mΩ

780mΩ

380mΩ

380mΩ

280mΩ

780mΩ

-

70V

70V

45V

45V

45V

45V

45V

OUT1, 2, 5, 6

-

-

OUT3, OUT4

OUT7, OUT8

X

-

OUT9, OUT10

OUT11...OUT14

OUT15, OUT16

OUT17, OUT18 *)

X

X

*) only serial control possible (via SPI)

Parallel connection of power stages is possible (see 1.13)

Internal short-circuit protection

Phase relation: non-inverting (exception: IN8->OUT8 is inverting)

1.1.2 Diagnostic Features

The following types of error can be detected:

Short-circuit to UBatt (SCB)

Short-circuit to ground (SCG)

Open load (OL)

Overtemperature (OT)

Individual detection for each output.

Serial transmission of the error code via SPI.

1.1.3 VDD-Monitoring

Low signal at pin ABE and shut-off of the power stages if VDD is out of the permitted range.

Exception: If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage

detection and not by undervoltage detection.

The state of VDD can be read out via SPI.

1.1.4 µsec-bus

Alternatively to the parallel and SPI control of the power stages, a high speed serial bus inter-

face can be configured as control of the power stages OUT1...OUT7 and OUT9...OUT16.

1.1.5 Power Stage OUT8

OUT8 can be controlled by SPI or by the pin IN8 only. When controlled by IN8 this power stage

is functional if the voltage at the pin VDD is above 3,5V. OUT8 will not be reset by RST. In

SPI mode the power stage is fully supervised by the VDD-monitor.

Final Data Sheet

2

V4.2, 2003-08-29

INFINEON [ Infineon ]

INFINEON [ Infineon ]