| 型号: | TLD7002-16ES |

| PDF下载: | 下载PDF文件 查看货源 |

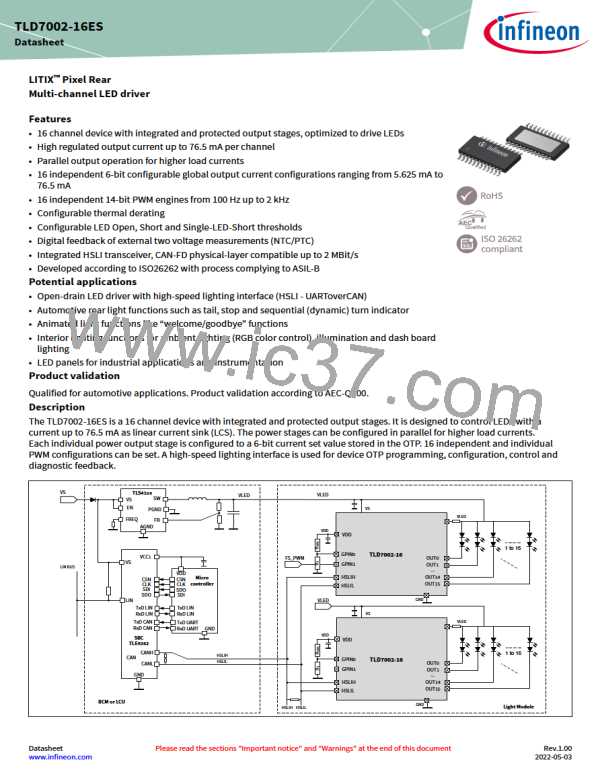

| 内容描述: | [The TLD7002-16ES is a 16 channel device with integrated and protected output stages. It is designed to control LEDs with a current up to 76.5 mA as linear current sink (LCS). The power stages can be configured in parallel for higher load currents. Each individual power output stage is configured to a 6-bit current set value stored in the OTP. 16 independent and individual PWM configurations can be set. A high-speed lighting interface is used for device OTP programming, configuration, control and] |

| 分类和应用: | |

| 文件页数/大小: | 82 页 / 3105 K |

| 品牌: |  INFINEON [ Infineon ] INFINEON [ Infineon ] |

专业IC领域供求交易平台:提供全面的IC Datasheet资料和资讯,Datasheet 1000万数据,IC品牌1000多家。