TLD7002-16ES

Datasheet

9 Communication interface

9

Communication interface

The device provides a UART-based protocol HSLI, where the LCU can write and read registers to and from each device

sharing the same bus.

The device provides the OTP programming and OTP emulation functions via the HSLI interface.

9.1

Protocol layer - High Speed Lighting Interface

General description

9.1.1

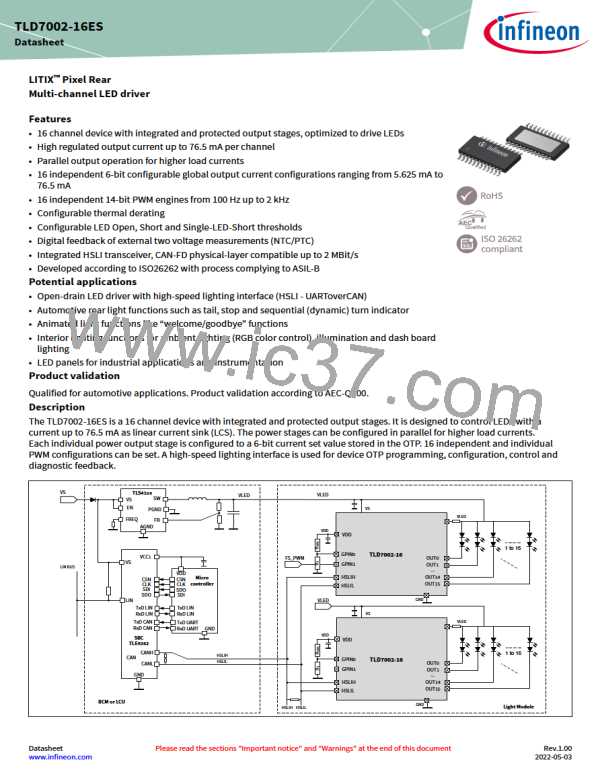

The High-speed Lighting Interface (HSLI) is a digital interface for high performance automotive applications. The

interface data link layer is based on a standard universal asynchronous receiver transmitter (UART) bit stream. The

protocol is designed to support direct device-to-µC connections as well as CAN-FD transceivers to implement a robust

connection scheme for remote control applications. Thanks to the lean protocol implementation, high update rates

can be achieved despite limited bandwidth especially with remote interfaces.

9.1.2

Main features

The HSLI is a cost efficient interface for high performance automotive applications. HSLI can be used as highly flexible

interface for transferring data.

•

•

•

•

•

Single master, multiple slave concept

Synchronization of single or multiple slaves

Supports bus configurations with up to 31 addressable slaves and 1 broadcast address

Bidirectional communication

Auto-bit rate detection within the range from 200 kbit/s up to 2 Mbit/s when LP_INIT='0' or up to 500 kbit/s when

LP_INIT='1'.

9.1.3

Frame structure

The frame consists of a number of bytes:

•

•

•

•

one sync byte

one master request

followed by 0 to n master data bytes

and 0 to n slave data bytes

The structure of a full communication frame is shown below:

Figure 17

Structure of a frame

9.1.4

HSLI interframe delay

The HSLI aborts processing the communication when no dominant ("0") bus communication occurred longer than

the interfame delay tframedly. The master needs to wait longer than tframedly between two consecutive frames.

The interframe delay is configurable via the OTP according to following table:

Datasheet

47

Rev.1.00

2022-05-03

INFINEON [ Infineon ]

INFINEON [ Infineon ]