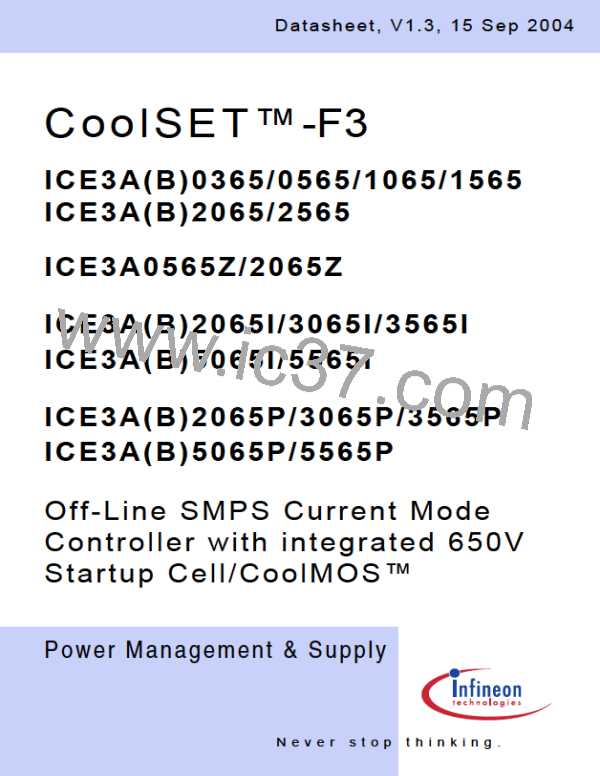

CoolSET™-F3

Functional Description

Once the malfunction condition is removed, this block maximum charge current in the very first stage when

will then turn back on. The recovery from Auto Restart VSoftS is below 1V, is limited to 1.32mA.

Mode does not require disconnecting the SMPS from

the AC line

When Active Burst Mode is entered, the internal Bias is

switched off in order to reduce the current consumption

VSoftS

to below 1.05mA while keeping the Voltage Reference

active as this is necessary in this mode.

max. Startup Phase

5.4V

4V

3.3

Startup Phase

1V

max. Soft Start Phase

6.5V

3.25k

DCmax

t

R

T2

SoftS

DC

1

T3

1V

DC

2

SoftS

C

SoftS

Soft Start

Soft-Start

t1

t2 t

Comparator

Gate Driver

C7

&

Figure 8

Startup Phase

G7

By means of this extra charge stage, there is no delay

in the beginning of the Startup Phase when there is still

no switching. Furthermore Soft Start is finished at 4V to

have faster the maximum power capability. The duty

cycles DC1 and DC2 are depending on the mains and

the primary inductance of the transformer. The

limitation of the primary current by DC2 is related to

VSoftS = 4V. But DC1 is related to a maximum primary

current which is limited by the internal Current Limiting

with CS = 1V. Therefore the maximum Startup Phase

is divided into a Soft Start Phase until t1 and a phase

from t1 until t2 where maximum power is provided if

demanded by the FB signal.

C2

4V

0.85V

CS

x3.7

PWM OP

Soft Start

Figure 7

At the beginning of the Startup Phase, the IC provides

a Soft Start duration whereby it controls the maximum

primary current by means of a duty cycle limitation. A

signal VSoftS which is generated by the external

capacitor CSofts in combination with the internal pull up

resistor RSoftS, determines the duty cycle until VSoftS

exceeds 4V.

When the Soft Start begins, CSoftS is immediately

charged up to approx. 1V by T2. Therefore the Soft

Start Phase takes place between 1V and 4V. Above

VSoftsS = 4V there is no longer duty cycle limitation

DCmax which is controlled by comparator C7 since

comparator C2 blocks the gate G7 (see Figure 6). This

Version 1.3

12

15 Sep 2004

INFINEON [ Infineon ]

INFINEON [ Infineon ]