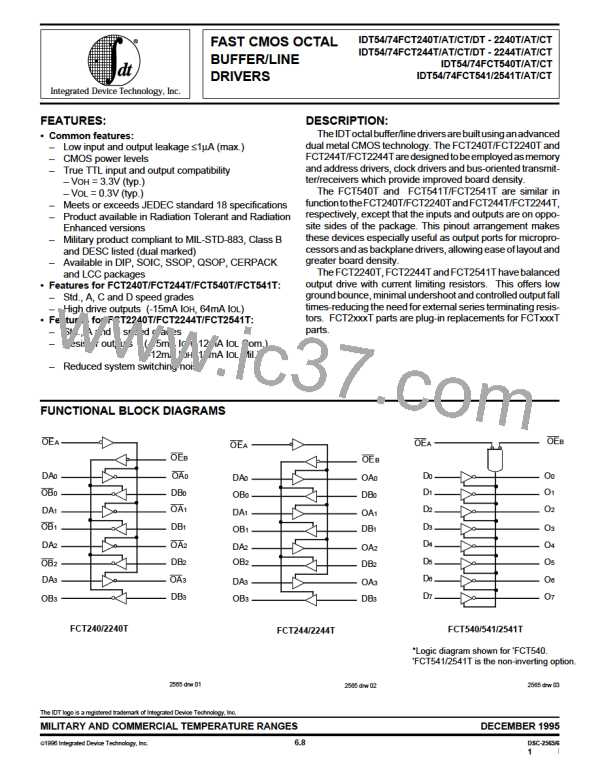

IDT54/74FCT240/244T/AT/CT/DT - 2240/2244T/AT/CT, IDT54/74FCT540/541/2541T/AT/CT

FAST CMOS OCTAL BUFFER/LINE DRIVER

MILITARY AND COMMERCIAL TEMPERATURE RANGES

TEST CIRCUITS AND WAVEFORMS

TEST CIRCUITS FOR ALL OUTPUTS

SWITCH POSITION

Test

Switch

VCC

7.0V

Open Drain

Disable Low

Closed

500Ω

500Ω

Enable Low

VOUT

VIN

Open

Pulse

Generator

All Other Tests

D.U.T.

2565 drw 14

DEFINITIONS:

CL= Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse

Generator.

50pF

C L

T

R

2565 drw 10

SET-UP, HOLD AND RELEASE TIMES

PULSE WIDTH

3V

DATA

1.5V

0V

INPUT

LOW-HIGH-LOW

PULSE

tH

tSU

1.5V

1.5V

3V

1.5V

0V

TIMING

INPUT

ASYNCHRONOUS CONTROL

tW

tREM

PRESET

CLEAR

ETC.

3V

1.5V

0V

HIGH-LOW-HIGH

PULSE

SYNCHRONOUS CONTROL

PRESET

2565 drw 12

3V

1.5V

CLEAR

tSU

tH

0V

CLOCK ENABLE

ETC.

2565 drw 11

PROPAGATION DELAY

ENABLE AND DISABLE TIMES

ENABLE

DISABLE

3V

1.5V

0V

3V

SAME PHASE

CONTROL

INPUT

1.5V

0V

INPUT TRANSITION

tPLH

tPHL

tPHL

tPZL

tPLZ

VOH

1.5V

VOL

OUTPUT

3.5V

1.5V

3.5V

VOL

OUTPUT

NORMALLY

LOW

SWITCH

CLOSED

tPLH

0.3V

0.3V

3V

1.5V

25605Vdrw 13

tPZH

tPHZ

OPPOSITE PHASE

INPUT TRANSITION

VOH

OUTPUT

NORMALLY

HIGH

SWITCH

OPEN

1.5V

0V

0V

2565 drw 14

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-

HIGH

2. Pulse Generator for All Pulses: Rate ≤ 1.0MHz; tF ≤ 2.5ns; tR ≤ 2.5ns

6.8

8

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]