932SQ420D

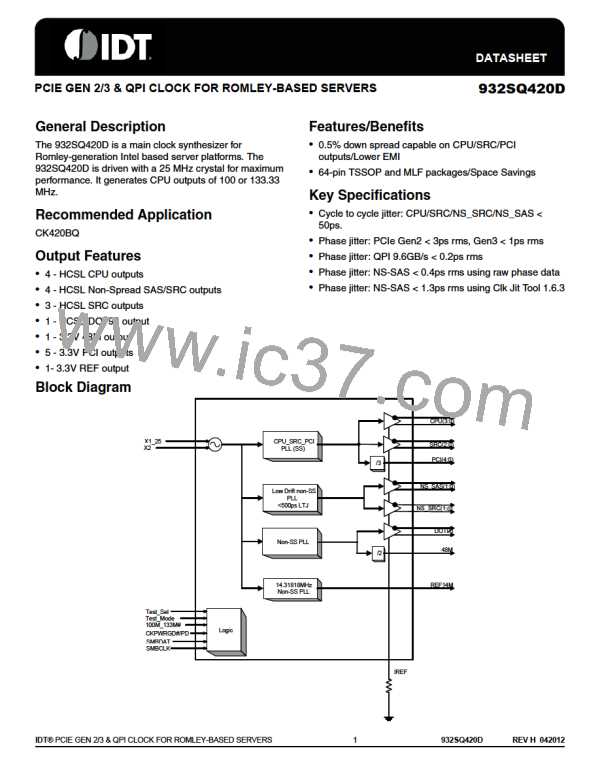

PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

Test Clarification Table

Comments

HW

SW

TEST

ENTRY BIT

B6b6

REF/N or

HI-Z

B6b7

TEST_MODE

HW PIN

X

TEST_SEL

HW P IN

OUTPUT

0

0

X

NORMAL

1

1

1

1

0

0

0

1

1

X

X

X

X

X

1

0

1

0

1

0

HI-Z

REF/N

REF/N

REF/N

HI-Z

Power-up w/ TEST_SEL = 1 (>2.0V) to enter test mode.

Cycle power to disable test mode.

If TEST_SEL HW pin is 0 during power-up,

test mode can be selected through B6b6.

If test mode is selected by B6b6, then B6b7

is used to select HI-Z or REF/N.

0

X

1

1

REF/N

TEST_Mode pin is not used.

Cycle power to disable test mode.

B6b6: 1= ENTER TEST MODE, Default = 0 (NORMAL OPERATION)

B6b7: 1= REF/N, Default = 0 (HI-Z)

Thermal Characteristics

Parameter

Symbol

Conditions

Min.

Typ. Max. Units

Thermal Resistance Junction to

Ambient

θ

Still air

68.2

63.3

59.6

32.5

51.5

° C/W

° C/W

° C/W

° C/W

° C/W

JA

θ

1 m/s air flow

2 m/s air flow

JA

θ

JA

Thermal Resistance Junction to Case

θ

JC

Thermal Resistance Junction to

Board

θ

JB

IDT® PCIE GEN 2/3 & QPI CLOCK FOR ROMLEY-BASED SERVERS

22

932SQ420D

REV H 042012

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]