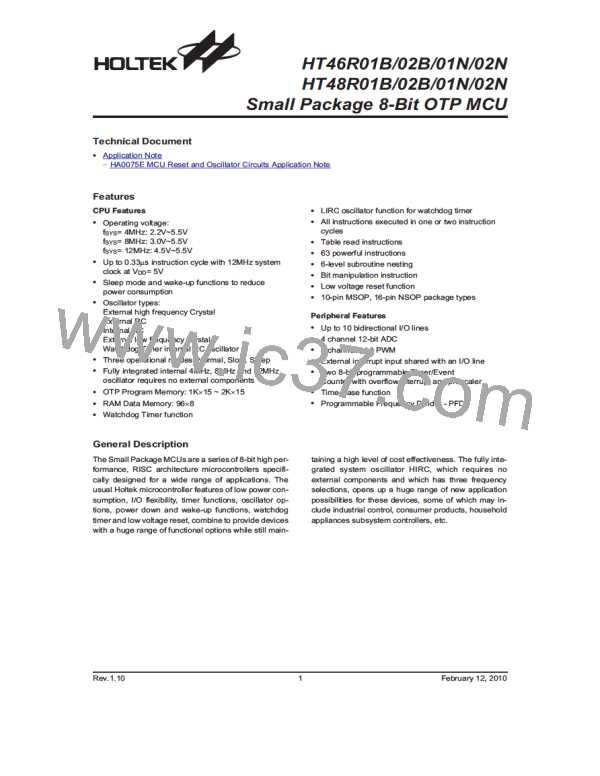

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

Note: I/T: Input type

O/T: Output type

OPT: Optional by configuration option (CO) or register option

PWR: Power

CO: Configuration option

ST: Schmitt Trigger input

CMOS: CMOS output

HT48R01N/HT48R02N

Pin Name Function

OPT

I/T

O/T

Description

PAPU

PAWK

PA0

PA0

ST

CMOS General purpose I/O. Register enabled pull-up and wake-up.

PAPU

PAWK

PA1

PFD

PA2

TC0

PA3

INT

ST

¾

CMOS General purpose I/O. Register enabled pull-up and wake-up.

CMOS PFD output

PA1/PFD

CTRL0

PAPU

PAWK

ST

ST

ST

ST

ST

ST

ST

¾

CMOS General purpose I/O. Register enabled pull-up and wake-up.

PA2/TC0

PA3/INT

External Timer 0 clock input

CMOS General purpose I/O. Register enabled pull-up and wake-up.

External interrupt input

CMOS General purpose I/O. Register enabled pull-up and wake-up.

External Timer 1 clock input

¾

¾

PAPU

PAWK

¾

¾

PAPU

PAWK

PA4

TC1

PA5

OSC2

PA6

PA4/TC1

PA5/OSC2

¾

¾

PAPU

PAWK

CMOS General purpose I/O. Register enabled pull-up and wake-up.

OSC Oscillator pin

CO

PAPU

PAWK

ST

CMOS General purpose I/O. Register enabled pull-up and wake-up.

PA6/OSC1

PA7/RES

OSC1

PA7

CO

PAWK

CO

OSC

ST

Oscillator pin

NMOS General purpose I/O. Register enabled wake-up.

Reset input

¾

RES

PB0

ST

¾

PB0

PB1

VDD

VSS

PBPU

PBPU

¾

ST

CMOS General purpose I/O. Register enabled.

CMOS General purpose I/O. Register enabled.

PB1

ST

VDD

VSS

PWR

PWR

Power supply

Ground

¾

¾

¾

Note: I/T: Input type

O/T: Output type

OPT: Optional by configuration option (CO) or register option

PWR: Power

CO: Configuration option

ST: Schmitt Trigger input

CMOS: CMOS output

Rev.1.10

6

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]