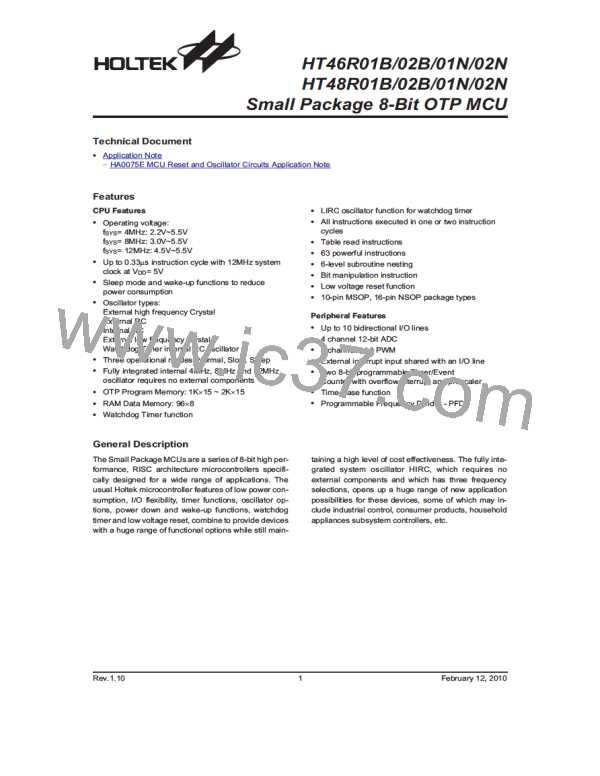

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

¨

HT48R01B/HT48R02B/HT48R01N/HT48R02N

Bit

Name

R/W

7

6

5

4

3

2

1

0

TBF

R/W

0

TBE

R/W

0

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

POR

Bit 7~6

Bit 5

unimplemented, read as ²0²

TBF: Time Base event interrupt request flag

0: inactive

1: active

Bit 4~2

Bit 1

unimplemented, read as ²0²

TBE: Time base event interrupt enable

0: disable

1: enable

Bit 0

unimplemented, read as ²0²

Timer/Event Counter Interrupt

Programming Considerations

For a Timer/Event Counter interrupt to occur, the global

interrupt enable bit, EMI, and the corresponding timer

interrupt enable bit, TnE, must first be set. An actual

Timer/Event Counter interrupt will take place when the

Timer/Event Counter request flag, TnF, is set, a situation

that will occur when the relevant Timer/Event Counter

overflows. When the interrupt is enabled, the stack is

not full and a Timer/Event Counter n overflow occurs, a

subroutine call to the relevant timer interrupt vector, will

take place. When the interrupt is serviced, the timer in-

terrupt request flag, TnF, will be automatically reset and

the EMI bit will be automatically cleared to disable other

interrupts.

By disabling the interrupt enable bits, a requested inter-

rupt can be prevented from being serviced, however,

once an interrupt request flag is set, it will remain in this

condition in the interrupt register until the corresponding

interrupt is serviced or until the request flag is cleared by

a software instruction.

It is recommended that programs do not use the ²CALL

subroutine² instruction within the interrupt subroutine.

Interrupts often occur in an unpredictable manner or

need to be serviced immediately in some applications. If

only one stack is left and the interrupt is not well con-

trolled, the original control sequence will be damaged

once a ²CALL subroutine² is executed in the interrupt

subroutine.

Time Base Interrupt

All of these interrupts have the capability of waking up

the processor when in the Sleep Mode.

For a time base interrupt to occur the global interrupt en-

able bit EMI and the corresponding interrupt enable bit

TBE, must first be set. An actual Time Base interrupt will

take place when the time base request flag TBF is set, a

situation that will occur when the Time Base overflows.

When the interrupt is enabled, the stack is not full and a

time base overflow occurs a subroutine call to time base

vector will take place. When the interrupt is serviced, the

time base interrupt flag. TBF will be automatically reset

and the EMI bit will be automatically cleared to disable

other interrupts.

Only the Program Counter is pushed onto the stack. If

the contents of the register or status register are altered

by the interrupt service program, which may corrupt the

desired control sequence, then the contents should be

saved in advance.

Rev.1.10

52

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]