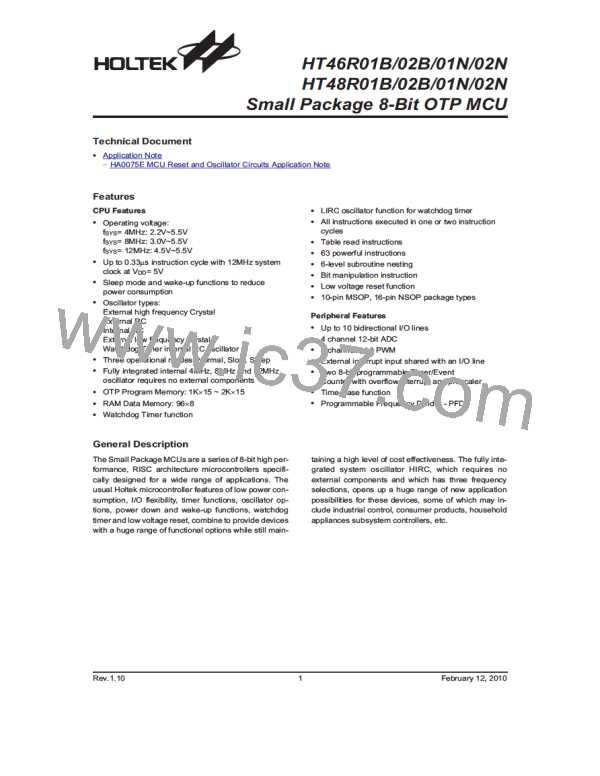

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

·

INTC0 Register

Bit

Name

R/W

7

6

5

4

INTF

R/W

0

3

2

1

INTE

R/W

0

0

T1F

R/W

0

T0F

R/W

0

T1E

R/W

0

T0E

R/W

0

EMI

R/W

0

¾

¾

¾

POR

Bit 7

Bit 6

unimplemented, read as ²0²

T1F: Timer/Event Counter 1 interrupt request flag

0: inactive

1: active

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

T0F: Timer/Event Counter 0 interrupt request flag

0: inactive

1: active

INTF: External interrupt request flag

0: inactive

1: active

T1E: Timer/Event Counter 1 interrupt enable

0: disable

1: enable

T0E: Timer/Event Counter 0 interrupt enable

0: disable

1: enable

INTE: external interrupt enable

0: disable

1: enable

EMI: Master interrupt global enable

0: disable

1: enable

·

INTC1 Register

¨

HT46R01B/HT46R02B/HT46R01N/HT46R02N

Bit

Name

R/W

7

6

5

4

3

2

1

0

TBF

R/W

0

ADF

R/W

0

TBE

R/W

0

ADE

R/W

0

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

POR

Bit 7~6

unimplemented, read as ²0²

Bit 5

TBF: Time Base event interrupt request flag

0: inactive

1: active

Bit 4

ADF: A/D Conversion interrupt request flag

0: inactive

1: active

Bit 3~2

Bit 1

unimplemented, read as ²0²

TBE: Time base event interrupt enable

0: disable

1: enable

Bit 0

ADE: A/D Conversion interrupt enable

0: disable

1: enable

Rev.1.10

51

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]