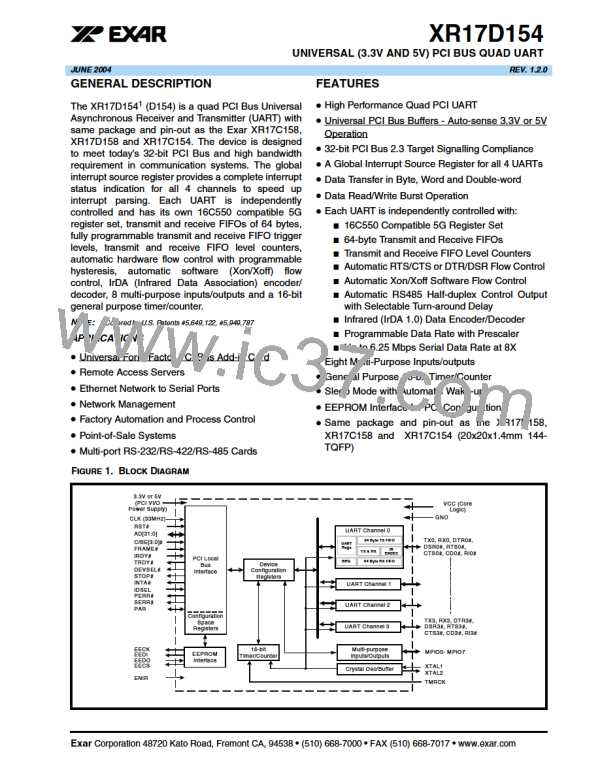

XR17D154

xr

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

FIGURE 26. TRANSMIT DATA INTERRUPT AT TRIGGER LEVEL

START

BIT

STOP

BIT

DATA BITS (5-8)

TX Data

D0

D1

D2

D3

D4

D5

D6

D7

PARITY

BIT

NEXT

5 DATA BITS

DATA

START

BIT

6 DATA BITS

7 DATA BITS

Clear at

Above

Trigger Level

TX Interrupt at

Transmit Trigger Level

Set at Below

Trigger Level

BAUD RATE CLOCK of 16X or 8X

TXNOFIFO-1

FIGURE 27. RECEIVE DATA READY INTERRUPT AT TRIGGER LEVEL

START

BIT

STOP

BIT

DATA BITS (5-8)

RX Data Input

D0

D1

D2

D3

D4

D5

D6 D7

First byte that

reaches the

trigger level

PARITY

BIT

RX Data Ready Interrupt at

Receive Trigger Level

De-asserted at

below trigger level

Asserted at

above trigger

level

RXFIFO1

64

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]