xr

XR17D154

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

TABLE OF CONTENTS

GENERAL DESCRIPTION................................................................................................. 1

APPLICATIONS ............................................................................................................................................... 1

FEATURES......................................................................................................................... 1

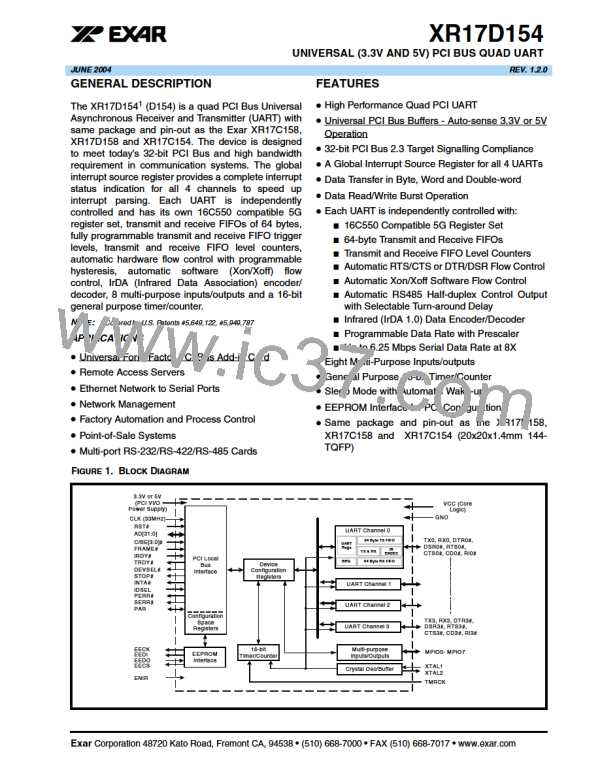

FIGURE 1. BLOCK DIAGRAM ............................................................................................................................................................. 1

FIGURE 2. PIN OUT OF THE DEVICE.................................................................................................................................................. 2

ORDERING INFORMATION ................................................................................................................................ 2

PIN DESCRIPTIONS.......................................................................................................... 3

PCI LOCAL BUS INTERFACE .................................................................................................................... 3

MODEM OR SERIAL I/O INTERFACE........................................................................................................ 3

ANCILLARY SIGNALS ................................................................................................................................ 4

FUNCTIONAL DESCRIPTION........................................................................................... 7

PCI Local Bus Interface............................................................................................................................................... 7

PCI Local Bus Configuration Space Registers............................................................................................................ 7

EEPROM Interface...................................................................................................................................................... 7

1.0 APPLICATION EXAMPLES .................................................................................................................. 8

TABLE 1: VALID COMBINATIONS OF VCC AND VIO SUPPLY VOLTAGES .............................................................................................. 8

FIGURE 3. TYPICAL APPLICATION FOR A UNIVERSAL ADD-IN CARD .................................................................................................... 8

FIGURE 4. TYPICAL APPLICATIONS IN AN EMBEDDED SYSTEM............................................................................................................ 9

2.0 XR17D154 REGISTERS ...................................................................................................................... 10

2.1 PCI LOCAL BUS CONFIGURATION SPACE REGISTERS .......................................................................... 10

FIGURE 5. THE XR17D154 REGISTER SETS .................................................................................................................................. 10

TABLE 2: PCI LOCAL BUS CONFIGURATION SPACE REGISTERS....................................................................................................... 11

2.2 DEVICE CONFIGURATION REGISTER SET ................................................................................................ 12

TABLE 3: XR17D154 DEVICE CONFIGURATION REGISTERS............................................................................................................. 13

TABLE 4: DEVICE CONFIGURATION REGISTERS SHOWN IN BYTE ALIGNMENT ................................................................................... 14

TABLE 5: DEVICE CONFIGURATION REGISTERS SHOWN IN DWORD ALIGNMENT .............................................................................. 14

2.2.1 THE INTERRUPT STATUS REGISTER ..................................................................................................................... 15

FIGURE 6. THE GLOBAL INTERRUPT REGISTER, INT0, INT1, INT2 AND INT3.................................................................................. 16

TABLE 6: UART CHANNEL [3:0] INTERRUPT SOURCE ENCODING..................................................................................................... 16

2.2.2 GENERAL PURPOSE 16-BIT TIMER/COUNTER [TIMERMSB, TIMELSB, TIMER, TIMECNTL] (DEFAULT 0XXX-XX-

00-00) ............................................................................................................................................................................. 17

TABLE 7: UART CHANNEL [3:0] INTERRUPT CLEARING: .................................................................................................................. 17

FIGURE 7. TIMER/COUNTER CIRCUIT............................................................................................................................................... 17

TABLE 8: TIMER CONTROL REGISTERS ...................................................................................................................................... 17

2.2.3 8XMODE [7:0] - (DEFAULT 0X00) ............................................................................................................................. 18

2.2.4 REGA [15:8] RESERVED ........................................................................................................................................... 18

2.2.5 RESET [23:16] - (DEFAULT 0X00)............................................................................................................................. 18

2.2.6 SLEEP [31:24] - (DEFAULT 0X00)............................................................................................................................ 19

2.2.7 DEVICE IDENTIFICATION AND REVISION............................................................................................................... 20

2.2.9 MULTI-PURPOSE INPUTS AND OUTPUTS.............................................................................................................. 20

2.2.8 REGB REGISTER ....................................................................................................................................................... 20

2.2.10 MPIO REGISTER ...................................................................................................................................................... 21

FIGURE 8. MULTIPURPOSE INPUT/OUTPUT INTERNAL CIRCUIT........................................................................................................... 21

3.0 CRYSTAL OSCILLATOR / BUFFER ................................................................................................... 23

FIGURE 9. TYPICAL OSCILLATOR CONNECTIONS............................................................................................................................... 23

FIGURE 10. EXTERNAL CLOCK CONNECTION FOR EXTENDED DATA RATE........................................................................................ 23

4.0 TRANSMIT AND RECEIVE DATA ...................................................................................................... 24

4.1 DATA LOADING AND UNLOADING VIA 32-BIT PCI BURST TRANSFERS ............................................... 24

4.1.1 NORMAL RX FIFO DATA UNLOADING AT LOCATIONS 0X100, 0X300, 0X500, 0X700....................................... 24

4.1.2 SPECIAL RX FIFO DATA UNLOADING AT LOCATIONS 0X180, 0X380, 0X580, AND 0X780.............................. 25

4.1.3 TX FIFO DATA LOADING AT LOCATIONS 0X100, 0X300, 0X500, 0X700............................................................. 26

4.2 FIFO DATA LOADING AND UNLOADING THROUGH THE UART CHANNEL REGISTERS, THR AND RHR IN

8-BIT FORMAT .............................................................................................................................................. 26

TABLE 9: TRANSMIT AND RECEIVE DATA REGISTER IN BYTE FORMAT, 16C550 COMPATIBLE ............................................................ 26

5.0 UART .................................................................................................................................................... 27

5.1 PROGRAMMABLE BAUD RATE GENERATOR ........................................................................................... 27

FIGURE 11. BAUD RATE GENERATOR ............................................................................................................................................. 27

5.2 TRANSMITTER ............................................................................................................................................... 28

5.2.1 TRANSMIT HOLDING REGISTER (THR) - WRITE-ONLY......................................................................................... 28

I

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]