XR17D154

xr

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

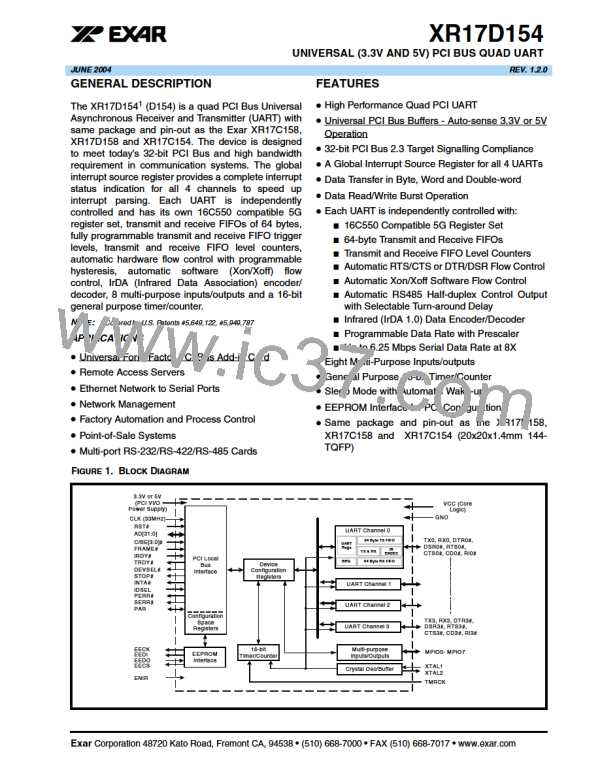

FIGURE 22. DEVICE CONFIGURATION REGISTERS, UART REGISTERS AND TRANSMIT DATA BURST WRITE OPERA-

TION

CLK

Host

1

7

2

3

4

5

6

8

9

10

11

FRAME#

Host

Data

DW ORD

Data

DW ORD

Data

DW ORD

Data

DW ORD

AD[31:0]

Address

Data DW O RD

Host

Target

Bus

CMD

C/BE[3:0]#

Host

Byte Enable# = DW ORD

IRDY#

Host

TRDY#

Target

DEVSEL#

Target

Data

Parity

Data

Parity

Data

Parity

Data

Parity

Data

Parity

Address

Parity

PAR

Host

Target

Active

Active

Active

Active

Active

PERR#

Target

SERR#

Active

Target

Note: PERR# and SERR are optional in a bus target application.

Even Parity is on AD[31:0], C/BE[3:0]#, and PAR

PCI_BW R

60

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]