| 型号: | XR17D154IVTR-F |

| PDF下载: | 下载PDF文件 查看货源 |

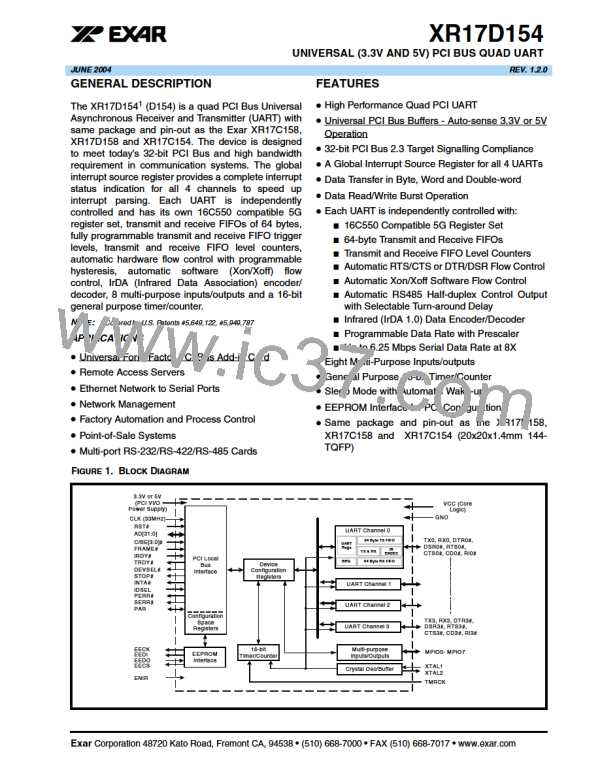

| 内容描述: | [Serial I/O Controller, 4 Channel(s), 0.78125MBps, CMOS, PQFP144, 20 X 20 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, TQFP-144] |

| 分类和应用: | PC |

| 文件页数/大小: | 69 页 / 840 K |

| 品牌: |  EXAR [ EXAR CORPORATION ] EXAR [ EXAR CORPORATION ] |

专业IC领域供求交易平台:提供全面的IC Datasheet资料和资讯,Datasheet 1000万数据,IC品牌1000多家。