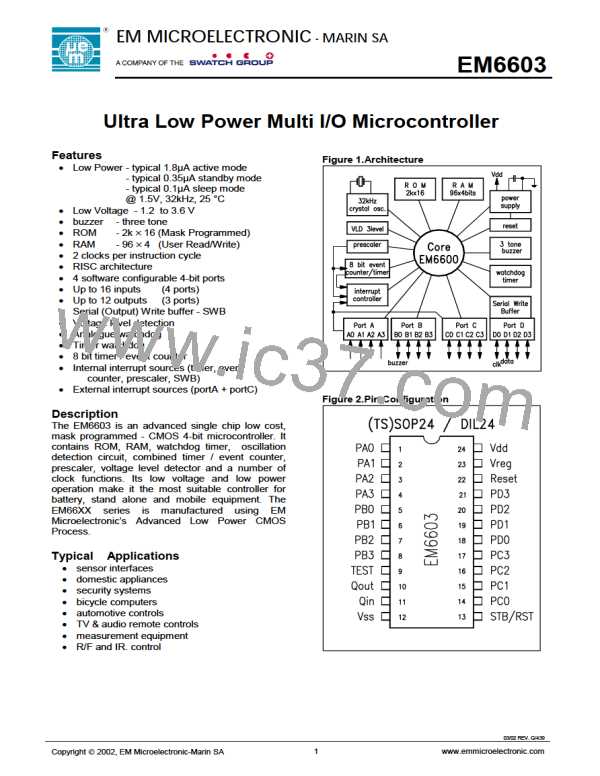

EM6603

4

Oscillator

A built-in crystal oscillator circuit generates the system operating clock for the CPU and peripheral circuits from an

externally connected crystal (typ. 32.768kHz) and trimmer capacitor (from Qin tw. Vss). The oscillator circuit is

supplied by the regulated voltage, Vreg. In SLEEP mode the oscillator is stopped.

With Fout bit in PA3cnt register we can put the system 32.768 Hz frequency on STB/RST pin as output.

4.1 Prescaler

The input to the prescaler is the system clock signal.

Table 6.Prescaler interrupt source

The prescaler consists of a fifteen (15) element divider

Interrupt frequency

PSF1

PSF0

chain which delivers clock signals for the peripheral

circuits such as the timer/counter, buzzer, I/O

debouncers and edge detectors, as well as generating

prescaler interrupts.

mask(no interrupt)

0

0

1

1

0

1

0

1

1 Hz

8 Hz

32 Hz

The frequency of prescaler interrupts is software selectable, as shown in Table 6.

Table 7. Prescaler control register - PRESC

Bit

Name

MTim

PRST

PSF1

PSF0

Reset

R/W

R/W

R/W

R/W

R/W

Description

3

0

-

Timer/Counter Interrupt Mask

Prescaler reset

2

1

0

0

Prescaler Interrupt select 1

Prescaler Interrupt select 0

0

5

Watchdog timer

If for any reason the CPU crashes, then the watchdog timer can detect this situation and output a system reset

signal. This function can be used to detect program overrun. For normal operation the watchdog timer must be

reset periodically by software at least once every three seconds (CLK = 32kHz) or a system reset signal is

generated to CPU and periphery. The watchdog is active during STANDBY. The watchdog reset function can be

deactivated by setting the NoWD bit to 1 in the Option register.

In worst case because of prescaler reset function WD time-out can come down to 2 seconds.

The watchdog timer is reset by writing 1 to the WDRST bit. Writing 0 to WDRST has no effect.

The watchdog timer also operates in STANDBY mode. It is therefore necessary to reset it if this mode continues

for more than three seconds. One method of doing this is to use the prescaler 1Hz interrupt such, that the

watchdog is reset every second.

Table 8.Watchdog register - WD

Bit

Name

WDRST

Slmask

WD1

Reset

R/W

R/W

R/W

R

Description

3

-

Watchdog timer reset

SLEEP mask bit

2

-

1

0

0

WD Timer data 1/4 Hz

WD Timer data 1/2 Hz

0

WD0

R

03/02 REV. G/439

8

www.emmicroelectronic.com

Copyright 2002, EM Microelectronic-Marin SA

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]