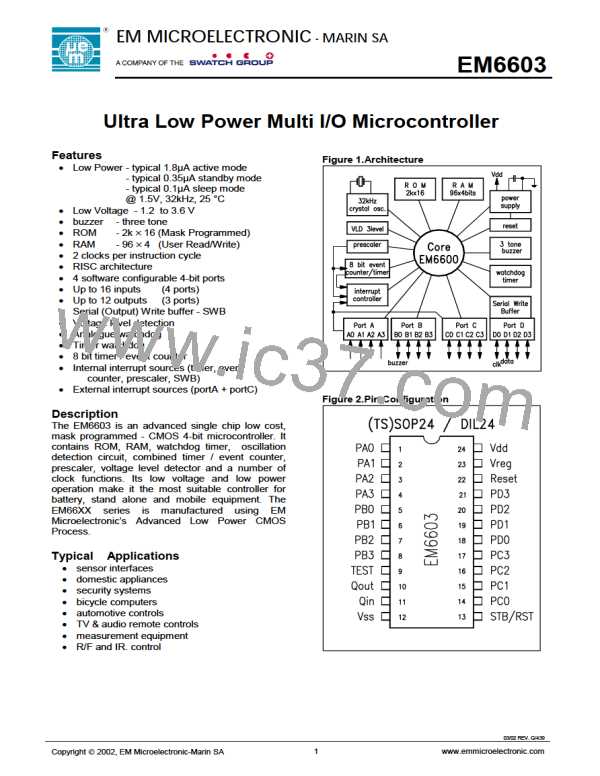

EM6603

Table 1. Pin Description

Pin Number Pin Name

Function

Remarks

1

2

port A, 0

port A, 1

port A, 2

port A, 3

port B, 0

port B, 1

port B, 2

port B, 3

test

input 0 port A

interrupt request; tvar 1

interrupt request; tvar 2

interrupt request; tvar 3

input 1 port A

3

input 2 port A

4

input 3 port A

interrupt request; event counter input

buzzer output

5

input / output 0 port B

input / output 1 port B

input / output 2 port B

input / output 3 port B

test input terminal

6

7

8

9

for EM test purpose only (internal pull-down)

Can accept trimming capacitor tw. Vss

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Qout/osc 1 crystal terminal 1

Qin/osc 2 crystal terminal 2 (input)

Vss

negative power supply terminal

STB/RST strobe / reset status

µC reset state + port B, C, D write

interrupt request

port C, 0

port C, 1

port C, 2

port C, 3

port D, 0

port D, 1

port D, 2

port D, 3

reset

input / output 0 port C

input / output 1 port C

input / output 2 port C

input / output 3 port C

input / output 0 port D

input / output 1 port D

input / output 2 port D

input / output 3 port D

reset terminal

interrupt request

interrupt request

interrupt request

SWB Serial Clock Output

SWB Serial Data Output

Active high (internal pull-down)

Needs typ. 100nF capacitor tw. Vss

Vreg

internal voltage regulator

positive power supply terminal

Vdd

Figure 3.Typical Configuration

For Vdd less then 1.4V it is recommended that Vdd is connected directly to Vreg

For Vdd>1.8V then the configuration shown in Fig.3 should be used.

03/02 REV. G/439

4

www.emmicroelectronic.com

Copyright 2002, EM Microelectronic-Marin SA

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]