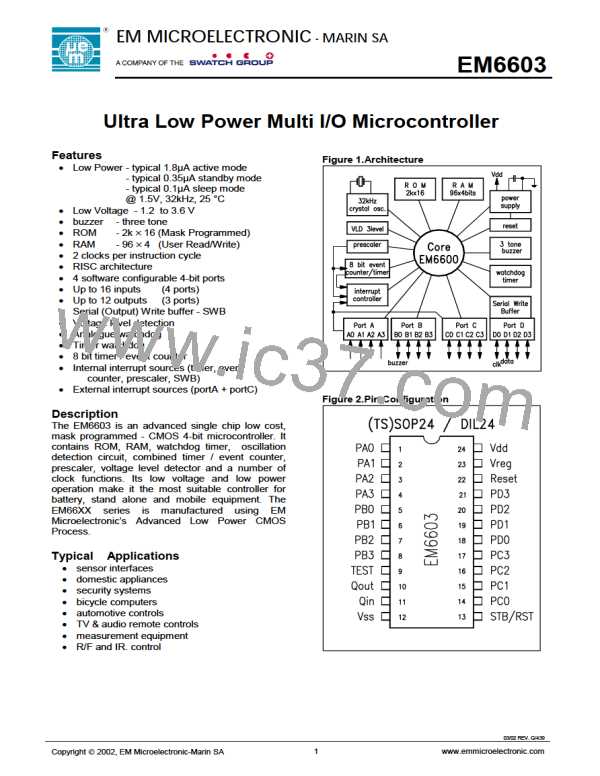

EM6603

Debounced PA0 is connected to CPU TestVar1

Debounced PA1 is connected to CPU TestVar2

Debounced PA2 is connected to CPU TestVar3

Figure 6.Port A

Additionally, PA3 can also be used as the input terminal for the event counter (see section 8).

The input port PA(0:3) also has individually selectable interrupts. Each port has its own interrupt mask bit in the

MPortA register. When an interrupt occurs inspection of the IRQpA and the IntRq registers allows the source

of the interrupt to be identified. The IRQpA register is automatically cleared by a RESET, by reading the

register. Reading IRQpA register also clears the INTPA flag in IntRq register. At initial RESET the MPortA is

set to 0, thus disabling any input interrupts.

See also section 9 for further details about the interrupt controller.

6.2 PortA registers

Table 11.PortA input status register - PortA

Bit

Name

PA3

PA2

PA1

PA0

Reset

R/W

R

Description

3

-

-

-

-

PA3 input status

PA2 input status

PA1 input status

PA0 input status

2

R

1

R

0

R

Table 12.PortA Interrupt request register - IRQpA

Bit

Name

Reset

R/W

Description

3

IRQpa3

IRQpa2

IRQpa1

IRQpa0

0

0

0

0

R

input PA3 interrupt request flag

input PA2 interrupt request flag

input PA1 interrupt request flag

input PA0 interrupt request flag

2

R

1

R

0

R

Table 13.PortA interrupt mask register - MportA

Bit

Name

MPA3

MPA2

MPA1

MPA0

Reset

R/W

R/W

R/W

R/W

R/W

Description

3

0

0

0

0

interrupt mask for input PA3

interrupt mask for input PA2

interrupt mask for input PA1

interrupt mask for input PA0

2

1

0

03/02 REV. G/439

10

www.emmicroelectronic.com

Copyright 2002, EM Microelectronic-Marin SA

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]