DS3251/DS3252/DS3253/DS3254

Table 17-I. SPI Interface Timing

(VDD = 3.3V M5%, TA = -40°C to +85°C.) (Figure 17-5)

PARAMETER (Note 1)

SCLK Frequency

SYMBOL

fBUS

tCYC

tSUC

tHDC

tCLKH

tCLKL

tSUI

MIN

TYP

MAX

UNITS

MHz

ns

ns

ns

10

SCLK Cycle Time

100

15

15

50

50

5

CS Setup to First SCLK Edge

CS Hold time After Last SCLK Edge

SCLK High Time

ns

SCLK Low Time

ns

SDI Data Setup Time

ns

SDI Data Hold Time

tHDI

15

0

ns

SDO Enable Time (High-Impedance to Output Active)

SDO Disable Time (Output Active to High-Impedance)

SDO Data Valid Time

tEN

ns

tDIS

25

40

ns

tDV

ns

SDO Data Hold Time After Update SCLK Edge

tHDO

5

ns

Note 1:

All timing is specified with 100pF load on all SPI pins.

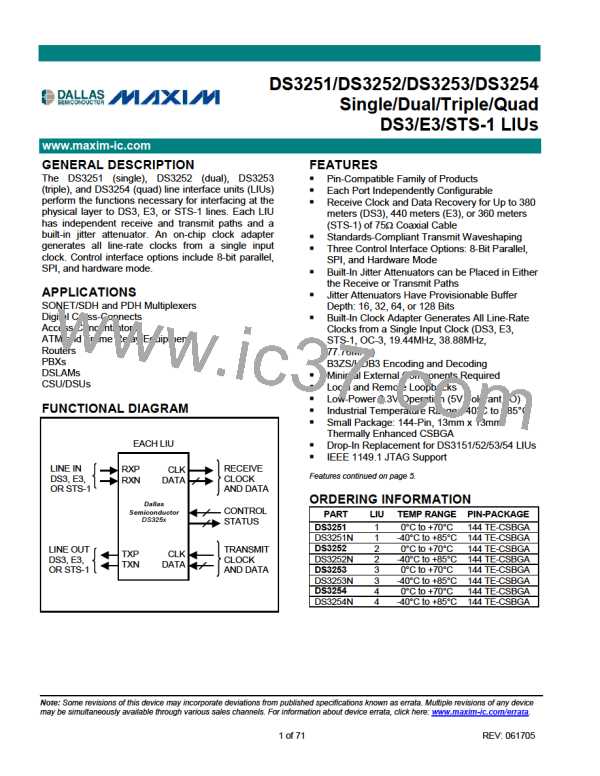

Figure 17-5. SPI Interface Timing Diagram

CPHA = 0

CS

tHDC

tSUC

tCYC

tCLKL

SCLK,

CPOL=0

tCLKH

tCLKL

SCLK,

CPOL=1

tCLKH

tSUI tHDI

SDI

tDV

tDIS

SDO

tEN

tHDO

CPHA = 1

CS

tHDC

tSUC

tCYC

tCLKL

SCLK,

CPOL=0

tCLKH

tCLKL

SCLK,

CPOL=1

tCLKH

tSUI tHDI

SDI

tDV

tDIS

SDO

tEN

tHDO

54 of 71

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]