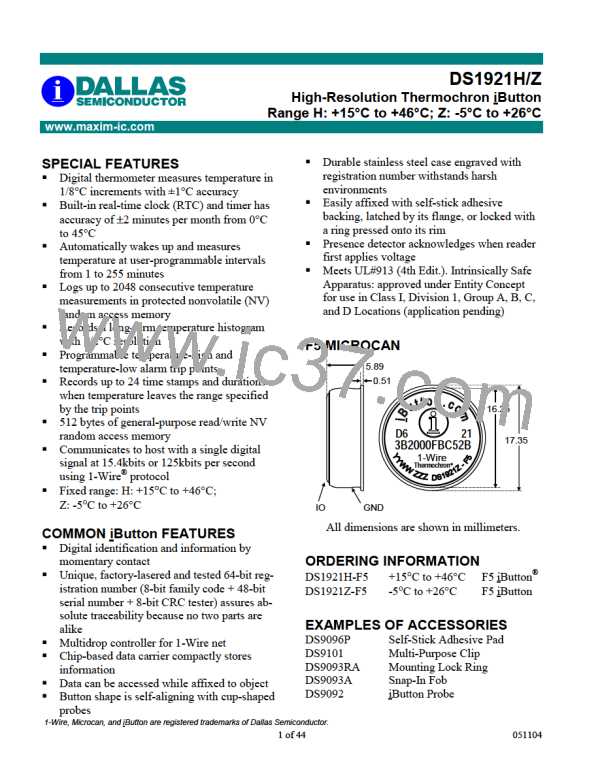

DS1921H/Z

STEP 2

Set the EMCLR bit to 1, enable the RTC and then execute the Clear Memory command. The RTC

oscillator must be stable before the Clear Memory command is issued. Wait 500 µs after issuing the Clear

Memory command before proceeding to Step 3. This results in the following data to be written to the

Status Register:

Address:

Data:

20Eh

40h

With only a single DS1921H/Z connected to the bus master, the communication of step 2 is as follows:

MASTER MODE

DATA (LSB FIRST)

(Reset)

(Presence)

CCh

COMMENTS

TX

RX

TX

TX

TX

TX

TX

TX

RX

TX

TX

RX

RX

RX

RX

TX

RX

TX

TX

TX

TX

TX

TX

RX

TX

TX

TX

RX

Reset pulse (480µs to 960µs)

Presence pulse

Issue Skip ROM command

Issue Write Scratchpad command

TA1, beginning offset = 0Eh

TA2, address = 020Eh

Write status byte to scratchpad

Reset pulse

0Fh

0Eh

02h

40h

(Reset)

(Presence)

CCh

Presence pulse

Issue Skip ROM command

Issue Read Scratchpad command

Read TA1, beginning offset = 0Eh

Read TA2, address = 020Eh

Read E/S, ending offset = 0Eh, flags = 0h

Read scratchpad data and verify

Reset pulse

AAh

0Eh

02h

0Eh

40h

(Reset)

(Presence)

CCh

Presence pulse

Issue Skip ROM command

Issue Copy Scratchpad command

TA1

55h

0Eh

TA2

E/S

(AUTHORIZATION CODE)

02h

0Eh

(Reset)

(Presence)

CCh

Reset pulse

Presence pulse

Issue Skip ROM command

Issue Clear Memory command

Reset pulse

3Ch

(Reset)

(Presence)

Presence pulse

37 of 44

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]