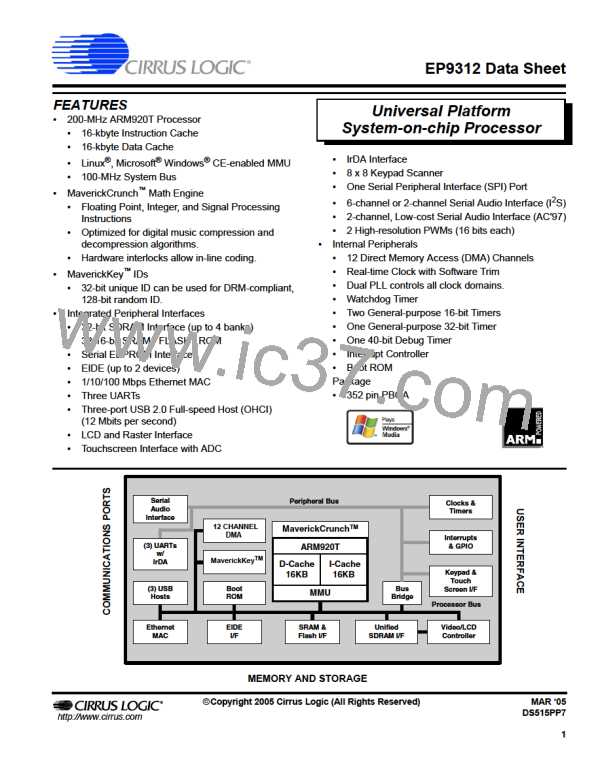

EP9312

Universal Platform SOC Processor

Dual LED Drivers

Table M. PLL and Clocking Pin Assignments

Two pins are assigned specifically to drive external

LEDs.

Pin Mnemonic

Pin Name - Description

XTALI

Main Oscillator Input

XTALO

Main Oscillator Output

Main Oscillator Power

Main Oscillator Ground

Table O. Dual LED Pin Assignments

Pin Name -

VDD_PLL

GND_PLL

Pin Mnemonic

Alternative Usage

Description

GRLED

Green LED

Red LED

General Purpose I/O

General Purpose I/O

Timers

REDLED

The Watchdog Timer ensures proper operation by

requiring periodic attention to prevent a reset-on-time-

out.

General Purpose Input/Output (GPIO)

The 16 EGPIO pins may each be configured individually

as an output, an input, or an interrupt input.

Two 16-bit timers operate as free-running down counters

or as periodic timers for fixed-interval interrupts and have

a range of 0.03 ms to 4.27 seconds.

There are 23 pins that may alternatively be used as input,

output, but do not support interrupts. These pins are:

One 32-bit timer, plus a 6-bit prescale counter, has a

range of 0.03 µs to 73.3 hours.

• Key Matrix ROW[7:0], COL[7:0]

• Ethernet MDIO

• Both LED Outputs

• Two-wire Clock and Data

• SLA [1:0]

One 40-bit debug timer, plus a 6-bit prescale counter, has

a range of 1.0 µs to 12.7 days.

Interrupt Controller

6 pins may alternatively be used as inputs only:

The interrupt controller allows up to 64 interrupts to

generate an Interrupt Request (IRQ) or Fast Interrupt

Request (FIQ) signal to the processor core. Thirty-two

hardware priority assignments are provided for assisting

IRQ vectoring, and two levels are provided for FIQ

vectoring. This allows time-critical interrupts to be

processed in the shortest time possible. Internal

interrupts may be programmed as active high or active

low level sensitive inputs. External interrupts may be

programmed as active-high level-sensitive, active-low

• CTSn, DSRn / DCDn

• 4 Interrupt Lines

2 pins may alternatively be used as outputs only:

• RTSn

• ARSTn

Table P. General Purpose Input/Output Pin Assignment

Pin Mnemonic

Pin Name - Description

level-sensitive,

triggered, or combined rising/falling-edge-triggered.

rising-edge-triggered,

falling-edge-

Expanded General Purpose Input / Output

Pins with Interrupts

EGPIO[15:0]

•

•

•

•

•

Supports 64 interrupts from a variety of sources (such

as UARTs, GPIO, and key matrix)

Reset and Power Management

Routes interrupt sources to either the ARM920T’s

IRQ or FIQ (Fast IRQ) inputs

The chip may be reset through the PRSTn pin or through

the open drain common reset pin, RSTOn.

Four dedicated off-chip interrupt lines INT[3:0]

operate as level-sensitive interrupts

Clocks are managed on a peripheral-by-peripheral basis

and may be turned off to conserve power.

Any of the 16 GPIO lines maybe configured to

generate interrupts

The processor clock is dynamically adjustable from 0 to

200 MHz (184 MHz for industrial conditions).

Software-supported priority mask for all FIQs and

IRQs

Table Q. Reset and Power Management Pin Assignments

Table N. External Interrupt Controller Pin Assignment

Pin Mnemonic

Pin Name - Description

Pin Mnemonic

Pin Name - Description

PRSTn

RSTOn

Power On Reset

INT[3:0]

External Interrupt 3-0

User Reset In/Out – Open Drain –

Preserves Real Time Clock value

10

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]