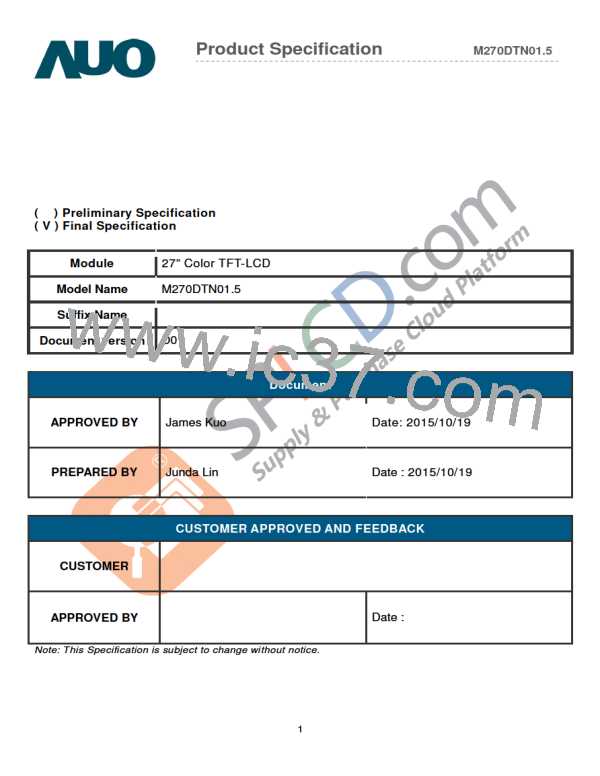

Product Specification

M270DTN01.5

3.2. Signal Description

CN1

PIN #

Symbol

R1_0N

DESCRIPTION

1

Negative LVDS differential data input (Port1 data)

Positive LVDS differential data input (Port1 data)

Negative LVDS differential data input (Port1 data)

Positive LVDS differential data input (Port1 data)

Negative LVDS differential data input (Port1 data)

Positive LVDS differential data input (Port1 data)

Ground

2

R1_0P

R1_1N

R1_1P

R1 2N

R1 2P

GND

3

4

5

6

7

8

R1_CLKN

R1_CLKP

GND

Negative LVDS differential clock input (Port1 clock)

Positive LVDS differential clock input (Port1 clock)

Ground

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

R2 3N

R2 3P

NC

Negative LVDS differential data input (Port1 data)

Positive LVDS differential data input (Port1 data)

No connection (for AUO test only. Do not connect)

No connection (for AUO test only. Do not connect)

Ground

NC

GND

R2_0N

R2_0P

R2_1N

R2_1P

R2 2N

R2 2P

GND

Negative LVDS differential data input (Port2 data)

Positive LVDS differential data input (Port2 data)

Negative LVDS differential data input (Port2 data)

Positive LVDS differential data input (Port2 data)

Negative LVDS differential data input (Port2 data)

Positive LVDS differential data input (Port2 data)

Ground

R2 CLKP

R2 CLKP

GND

Negative LVDS differential clock input (Port2 clock)

Positive LVDS differential clock input (Port2 clock)

Ground

R2_3N

R2_3P

NC

Negative LVDS differential data input (Port2 data)

Positive LVDS differential data input (Port2 data)

No connection (for AUO test only. Do not connect)

No connection (for AUO test only. Do not connect)

No connection (for AUO test only. Do not connect)

NC

NC

11

AUO [ AUO ]

AUO [ AUO ]