ATmega16/32/64/M1/C1

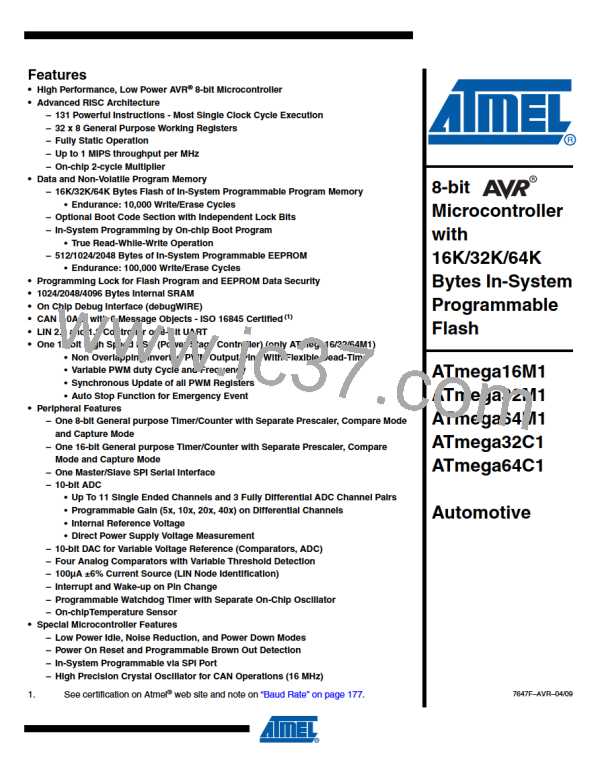

Figure 16-14. CAN Controller Interrupt Structure

CANGIE.4 CANGIE.5 CANGIE.3

ENTX

ENRX

ENERR

CANSIT 1/2

SIT[i]

CANSTMOB.6 TXOK[i]

CANSTMOB.5 RXOK[i]

CANSTMOB.4 BERR[i]

CANSTMOB.3 SERR[i]

CANSTMOB.2 CERR[i]

CANSTMOB.1 FERR[i]

CANSTMOB.0 AERR[i]

CANIE 1/2

IEMOB[i]

0

CANGIT.7

CANIT

i

CANGIE.7

CANGIE.2 CANGIE.1 CANGIE.6

ENBX ENERG ENBOFF

ENIT

CANGIT.4

BXOK

CAN IT

CANGIT.3

CANGIT.2

CANGIT.1

CANGIT.0

SERG

CERG

FERG

AERG

CANGIE.0

CANGIT.6

BOFFI

ENOVRT

OVR IT

CANGIT.5 OVRTIM

16.8.2

Interrupt Behavior

When an interrupt occurs, an interrupt flag bit is set in the corresponding MOb-CANSTMOB reg-

ister or in the general CANGIT register. If in the CANIE register, ENRX / ENTX / ENERR bit are

set, then the corresponding MOb bit is set in the CANSITn register.

To acknowledge a MOb interrupt, the corresponding bits of CANSTMOB register (RXOK,

TXOK,...) must be cleared by the software application. This operation needs a read-modify-write

software routine.

To acknowledge a general interrupt, the corresponding bits of CANGIT register (BXOK, BOF-

FIT,...) must be cleared by the software application. This operation is made writing a logical one

in these interrupt flags (writing a logical zero doesn’t change the interrupt flag value).

OVRTIM interrupt flag is reset as the other interrupt sources of CANGIT register and is also

reset entering in its dedicated interrupt handler.

When the CAN node is in transmission and detects a Form Error in its frame, a bit Error will also

be raised. Consequently, two consecutive interrupts can occur, both due to the same error.

When a MOb error occurs and is set in its own CANSTMOB register, no general error is set in

CANGIT register.

185

7647F–AVR–04/09

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]