ATmega16/32/64/M1/C1

16.7 Error Management

16.7.1

Fault Confinement

The CAN channel may be in one of the three following states:

• Error active (default):

The CAN channel takes part in bus communication and can send an active error frame when

the CAN macro detects an error.

• Error passive:

The CAN channel cannot send an active error frame. It takes part in bus communication, but

when an error is detected, a passive error frame is sent. Also, after a transmission, an error

passive unit will wait before initiating further transmission.

• Bus off:

The CAN channel is not allowed to have any influence on the bus.

For fault confinement, a transmit error counter (TEC) and a receive error counter (REC) are

implemented. BOFF and ERRP bits give the information of the state of the CAN channel. Setting

BOFF to one may generate an interrupt.

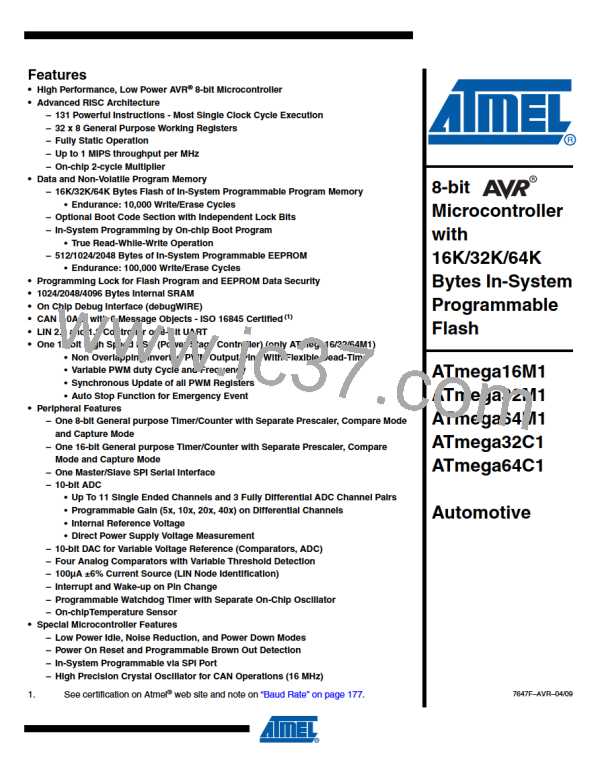

Figure 16-12. Line Error Mode

Reset

ERRP = 0

BOFF = 0

Error

Active

TEC > 127 or

128 occurrences

REC > 127

of 11 consecutive

recessive bit

TEC < 127 and

REC < 127

ERRP = 0

BOFF = 1

ERRP = 1

BOFF = 0

Bus

Off

Error

Passive

TEC > 255

interrupt - BOFFIT

Note:

More than one REC/TEC change may apply during a given message transfer.

16.7.2

Error Types

• BERR: Bit error. The bit value which is monitored is different from the bit value sent.

Note:

Exceptions:

- Recessive bit sent monitored as dominant bit during the arbitration field and the acknowl-

edge slot.

- Detecting a dominant bit during the sending of an error frame.

• SERR: Stuff error. Detection of more than five consecutive bit with the same polarity.

• CERR: CRC error (Rx only). The receiver performs a CRC check on every destuffed received

message from the start of frame up to the data field. If this checking does not match with the

destuffed CRC field, an CRC error is set.

• FERR: Form error. The form error results from one (or more) violations of the fixed form of

the following bit fields:

– CRC delimiter

– acknowledgement delimiter

183

7647F–AVR–04/09

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]