clear

clkTn

top

Clear TCNT2 (set all bits to zero).

Timer/Counter clock, referred to as clkT2 in the following.

Signalizes that TCNT2 has reached maximum value.

Signalizes that TCNT2 has reached minimum value (zero).

bottom

Depending on the mode of operation used, the counter is cleared, incremented, or dec-

remented at each timer clock (clkT2). clkT2 can be generated from an external or internal

clock source, selected by the Clock Select bits (CS22:0). When no clock source is

selected (CS22:0 = 0) the timer is stopped. However, the TCNT2 value can be accessed

by the CPU, regardless of whether clkT2 is present or not. A CPU write overrides (has

priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM21 and WGM20 bits

located in the Timer/Counter Control Register (TCCR2A) and the WGM22 located in the

Timer/Counter Control Register B (TCCR2B). There are close connections between

how the counter behaves (counts) and how waveforms are generated on the Output

Compare outputs OC2A and OC2B. For more details about advanced counting

sequences and waveform generation, see “Modes of Operation” on page 137.

The Timer/Counter Overflow Flag (TOV2) is set according to the mode of operation

selected by the WGM22:0 bits. TOV2 can be used for generating a CPU interrupt.

Output Compare Unit

The 8-bit comparator continuously compares TCNT2 with the Output Compare Register

(OCR2A and OCR2B). Whenever TCNT2 equals OCR2A or OCR2B, the comparator

signals a match. A match will set the Output Compare Flag (OCF2A or OCF2B) at the

next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare

Flag generates an Output Compare interrupt. The Output Compare Flag is automatically

cleared when the interrupt is executed. Alternatively, the Output Compare Flag can be

cleared by software by writing a logical one to its I/O bit location. The Waveform Gener-

ator uses the match signal to generate an output according to operating mode set by the

WGM22:0 bits and Compare Output mode (COM2x1:0) bits. The max and bottom sig-

nals are used by the Waveform Generator for handling the special cases of the extreme

values in some modes of operation (“Modes of Operation” on page 137).

Figure 56 shows a block diagram of the Output Compare unit.

134

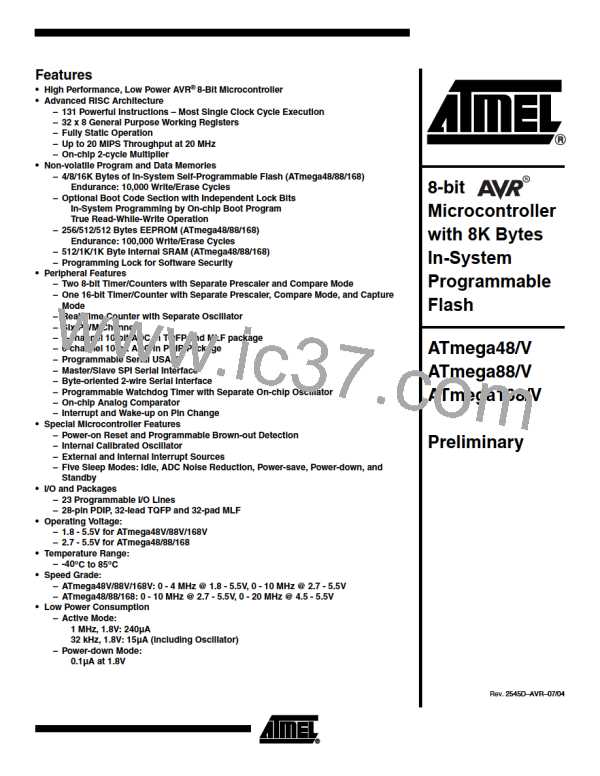

ATmega48/88/168

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]