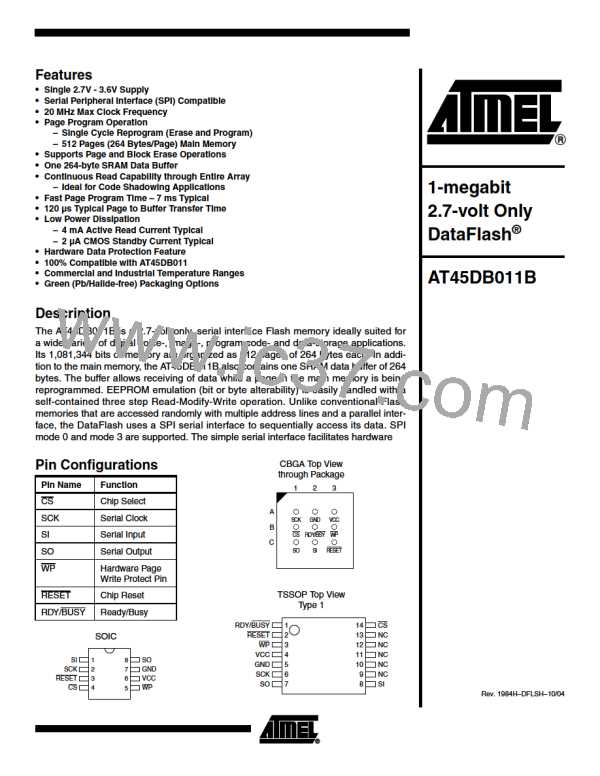

AT45DB011B

Reset Timing (Inactive Clock Polarity Low Shown)

CS

t

t

REC

CSS

SCK

t

RST

RESET

HIGH IMPEDANCE

HIGH IMPEDANCE

SO

SI

Note:

The CS signal should be in the high state before the RESET signal is deasserted.

Command Sequence for Read/Write Operations (Except Status Register Read)

SI

CMD

8 bits

8 bits

8 bits

MSB

r r r r r r X X

X X X X X X X X

Page Address

X X X X X X X X

LSB

Reserved for

Byte/Buffer Address

larger densities

(PA8-PA0)

(BA8-BA0/BFA8-BFA0)

Notes: 1. “r” designates bits reserved for larger densities.

2. It is recommended that “r” be a logical “0”.

3. For densities larger than 1M bit, the “r” bits become the most significant Page Address bit for the appropriate density.

15

1984H–DFLSH–10/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]