Isolated, Digital Output, Power Monitoring IC

with Zero-Crossing Detection, Overcurrent and Overvoltage Flagging

ACS37800

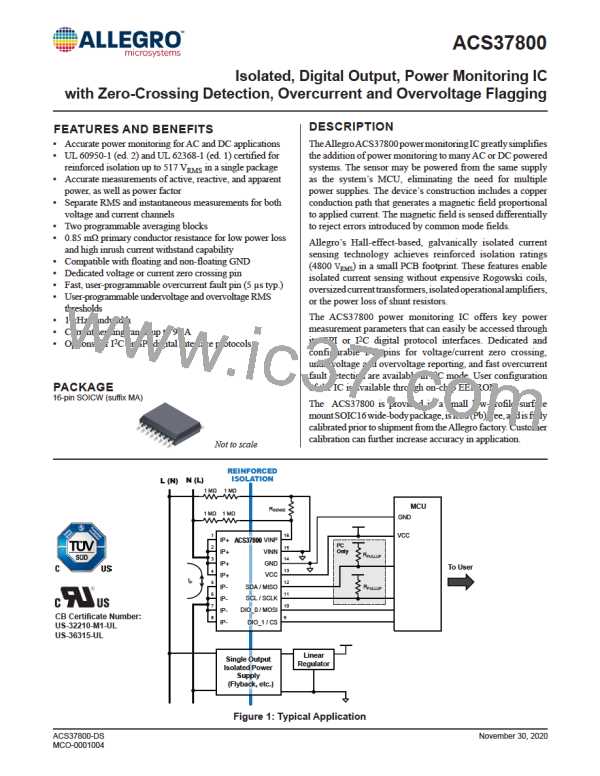

FUNCTIONAL BLOCK DIAGRAM

VCC

DIGITAL SYSTEM

Bandgap

Reference

SDA / MISO

SCL / SCLK

DIO_0 / MOSI

Temperature

Compensation

Logic

2

I C/SPI

Temperature

Sensor

To All

Communication

Subcircuits

EEPROM +

VINP

VINN

Charge Pump

V

ADC

ADC

DIO_1 / CS

I

Metrology

Engine

IP+

Fault Logic

Hall Sensor Array

GND

IP–

PINOUT DIAGRAM AND TERMINAL LIST

Terminal List Table

16 VINP

15 VINN

14 GND

13 VCC

IP+

IP+

IP+

IP+

IP-

1

2

3

4

5

6

7

8

Description

Number

Name

I2C

SPI

1, 2, 3, 4

IP+

IP-

Terminals for current being sensed; fused internally

Terminals for current being sensed; fused internally

5, 6, 7, 8

12 SDA / MISO

9

DIO_1/CS

DIO_0/MOSI

SCL /SCLK

SDA /MISO

VCC

Digital I/O 1

Digital I/O 0

SCL

Chip Select (CS)

MOSI

IP-

11 SCL / SCLK

10

11

12

13

14

15

16

IP-

10 DIO_0 / MOSI

SCLK

IP-

9

DIO_1 / CS

SDA

MISO

Device power supply terminal

Pinout Diagram

GND

Device ground terminal

Negative input voltage (always connect to GND)

Positive input voltage

VINN

VINP

4

Allegro MicroSystems

955 Perimeter Road

Manchester, NH 03103-3353 U.S.A.

www.allegromicro.com

ALLEGRO [ ALLEGRO MICROSYSTEMS ]

ALLEGRO [ ALLEGRO MICROSYSTEMS ]