A4931

3-Phase Brushless DC Motor Pre-Driver

Functional Block Diagram

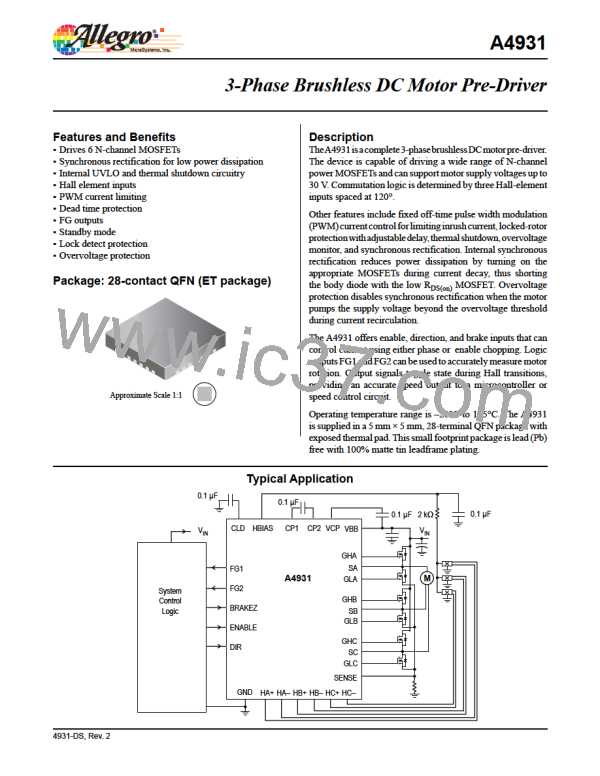

0.1 μF

0.1 μF

Lock

Detect

CLD

FG1

CHARGE PUMP

VCP

VBB

0.1 μF

HBIAS

HA+

VREG

2 kΩ

HALL

VIN

0.1 μF

OVP

HA-

VCP

VREG

Commun-

ication

GHA

SA

HB+

HB-

HALL

HALL

Logic

GHB

SB

GATE

DRIVE

HC+

HC-

GLB

GHC

SC

Control

Logic

GLC

FG1

FG2

GLA

BRAKEZ

DIR

SENSE

RSENSE

System

Logic

200 mV

ENABLE

VIN

GND

Terminal List

Number

Name

Description

Number

15

Name

Description

1

2

HA+

HA -

Hall input A

Hall input A

Hall input B

Hall input B

Hall input C

Hall input C

Ground

GLB

GLA

Low side gate drive B

Low side gate drive A

High side gate drive C

16

3

HB+

17

GHC

SC

4

HB -

18

High side source connection C

High side gate drive B

5

HC+

HC-

19

GHB

SB

6

20

High side source connection B

High side gate drive A

7

GND

HBIAS

CP1

21

GHA

SA

8

Hall bias power supply output

Charge pump capacitor terminal

Charge pump capacitor terminal

Supply voltage

22

High side source connection A

FG 1 speed control output (3 Φ inputs)

FG 2 speed control output (ΦA input)

Locked rotor detect timing capacitor

Logic input – motor direction

9

23

FG1

10

11

12

13

14

CP2

24

FG2

VBB

25

CLD

VCP

SENSE

GLC

Reservoir capacitor terminal

Sense resistor connection

Low side gate drive C

26

DIR

27

ENABLE

BRAKEZ

Logic input – external PWM control

Logic input – motor brake (active low)

28

Allegro MicroSystems, Inc.

115 Northeast Cutoff

3

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

ALLEGRO [ ALLEGRO MICROSYSTEMS ]

ALLEGRO [ ALLEGRO MICROSYSTEMS ]