[AK8975/C]

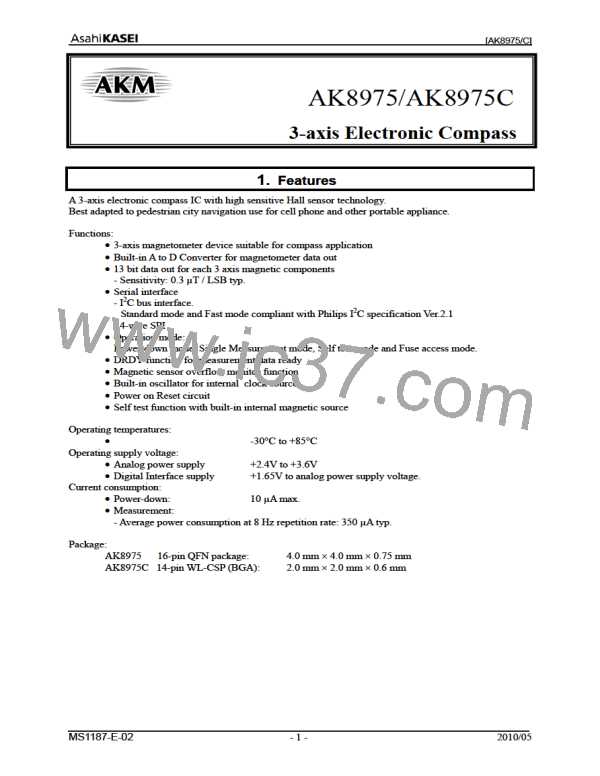

7.2.3. READ Instruction

When the R/W bit is set to "1", AK8975/C performs read operation.

If a master IC generates an acknowledge instead of a stop condition after AK8975/C transfers the data at a

specified address, the data at the next address can be read.

Address can be from 00H to 0CH and/or from 10H to 12H.When address is counted up to 0CH in the range of

00H to 0CH, the next address returns to 00H. When address is counted up to 12H in the range of 10H to 12H,

the next address returns to 10H.

AK8975/C supports one byte read and multiple byte read.

7.2.3.1. One Byte READ

AK8975/C has an address counter inside the LSI chip. In current address read operation, the data at an address

specified by this counter is read.

The internal address counter holds the next address of the most recently accessed address.

For example, if the address most recently accessed (for READ instruction) is address "n", and a current address

read operation is attempted, the data at address "n+1" is read.

In one byte read operation, AK8975/C generates an acknowledge after receiving a slave address for the READ

instruction (R/W bit="1"). Next, AK8975/C transfers the data specified by the internal address counter starting

with the next clock pulse, then increments the internal counter by one. If the master IC generates a stop

condition instead of an acknowledge after AK8975/C transmits one byte of data, the read operation stops.

S

S

T

O

P

T

A

R

T

R/W="1"

Slave

Address

Data(n)

Data(n+1)

Data(n+2)

Data(n+x)

S

P

SDA

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

Figure 7.10 One Byte READ

7.2.3.2. Multiple Byte READ

By multiple byte read operation, data at an arbitrary address can be read.

The multiple byte read operation requires to execute WRITE instruction as dummy before a slave address for

the READ instruction (R/W bit="1") is transmitted. In random read operation, a start condition is first

generated then a slave address for the WRITE instruction (R/W bit="0") and a read address are transmitted

sequentially.

After AK8975/C generates an acknowledge in response to this address transmission, a start condition and a

slave address for the READ instruction (R/W bit="1") are generated again. AK8975/C generates an

acknowledge in response to this slave address transmission. Next, AK8975/C transfers the data at the specified

address then increments the internal address counter by one. If the master IC generates a stop condition instead

of an acknowledge after data is transferred, the read operation stops.

S

T

A

R

T

S

T

A

R

T

S

T

O

P

R/W="0"

R/W="1"

Slave

Address

Register

Address(n)

Slave

Address

Data(n)

Data(n+1)

Data(n+x)

S

S

P

SDA

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

Figure 7.11 Multiple Byte READ

MS1187-E-02

- 21 -

2010/05

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]