ASAHI KASEI

[AK5385B]

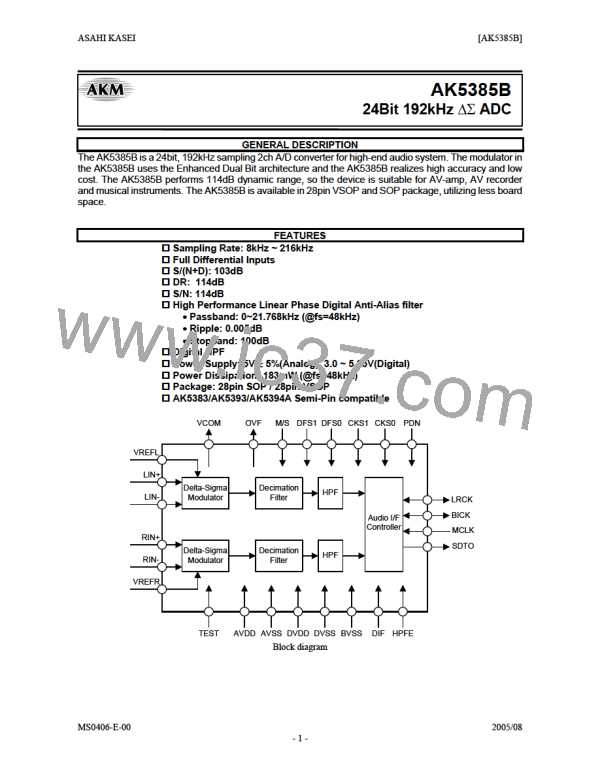

Compare PCB layout example between AK5385B and AK5394A

Analog Ground

Analog Ground

VREFL

0.1µ

0.1µ

0.1µ

0.1µ

0.1µ

10µ

10µ

10µ

10µ

10µ

10µ

1

2

3

4

5

6

7

8

9

VREFL+

VREFL-

VCOML

AINL+

AINL-

ZCAL

VD

VREFR+ 28

VREFR- 27

VCOMR 26

AINR+ 25

AINR- 24

VA 23

1

2

3

4

5

6

7

8

9

VREFR 28

AVSS 27

TEST 26

RIN+ 25

RIN- 24

(short)

(short)

AVSS

VCOM

LIN+

0.22µ

0.22µ

0.22µ

5V

Analog

5V

Analog

LIN-

0.1µ

CKS0

DVDD

DVSS

OVF

AVDD 23

AVSS 22

BVSS 21

DFS1 20

HPFE 19

DFS0 18

MCLK 17

CKS1 16

SDTO 15

3.0 ~ 5.25V

Digital

0.1µ

3.0 ~ 5.25V

Digital

0.1µ

AGND 22

BGND 21

DFS1 20

HPFE 19

DFS0 18

MCLK 17

FSYNC 16

SDATA 15

10µ

10µ

DGND

CAL

10µ

10µ

10 RSTN

10 PDN

11 DIF

11 SMODE2

12 SMODE1

13 LRCK

12 M/S

13 LRCK

14 BICK

14 SCLK

AK5394A

AK5394A

AK5385B

AK5385B

Pin #

1

VREFL+

VREFL

Lch Positive Voltage Reference Output Pin, 3.75V

Normally connected to AGND with a large

electrolytic capacitor and connected to VREFL−

with a 0.22µF ceramic capacitor.

Lch Voltage Reference Input Pin, AVDD

Normally, connected to AVSS with a 10µF

electrolytic capacitor and a 0.1µF ceramic capacitor.

AVSS

VREFL−

Analog Ground Pin

Lch Negative Voltage Reference Output Pin, 1.25V

Normally connected to AGND with a large

electrolytic capacitor and connected to VREFL+

with a 0.22µF ceramic capacitor.

2

6

ZCAL

CKS0

Master Clock Select 0 Pin

(Internal Pull-down Pin, typ. 100kΩ)

Zero Calibration Control Pin

This pin controls the calibration reference signal.

CAL

OVF

9

Calibration Active Signal Pin

Analog Input Overflow Detect Pin

SMODE2

Serial Interface Mode Select Pin

SMODE1

Serial Interface Mode Select Pin

FSYNC

DIF

11

12

Audio Interface Format Pin

M/S

Master / Slave Mode Pin

CKS1

16

Master Clock Select 1 Pin

(Internal Pull-down Pin, typ. 100kΩ)

AVSS

Frame Synchronization Signal Pin

VREFR−

Analog Ground Pin

Rch Negative Voltage Reference Output Pin, 1.25V

Normally connected to AGND with a large

electrolytic capacitor and connected to VREFR+

with a 0.22µF ceramic capacitor.

VCOMR

Rch Common Voltage Pin, 2.75V

27

26

28

TEST

Test Pin (Internal Pull-down Pin, typ. 100kΩ)

VREFR

Rch Voltage Reference Input Pin, AVDD

Normally, connected to AVSS with a 10µF

electrolytic capacitor and a 0.1µF ceramic capacitor.

VREFR+

Rch Positive Reference Output Voltage, 3.75V

Normally connected to AGND with a large

electrolytic capacitor and connected to VREFR−

with a 0.22µF ceramic capacitor.

MS0406-E-00

2005/08

- 5 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]