AD9228

A H C _ O S D

ꢀ 0

4 2 R 7

A H C _ I S D

ꢀ 0

4 2 R 0

A H C _ K L S C

ꢀ 0

4 2 R 8

A

_ C B H 1 C S

ꢀ 0

4 2 R 6

J401

PICVCC

1

2

PICVCC

GP1

GP0

3

5

4

6

GP1

GP0

MCLR/GP3

7

9

8

10

MCLR/GP3

ꢀ k 7 5 4 .

4 1 R 8

OPTIONAL

PIC PROGRAMMING HEADER

V

± 7 5 m = H N I = P O L H I

V 0 . V 5 - 5 2 .

2

P E O = S N L I A

V I E T G A E G N

V I E T G S I P O

V m 0 5 ± = L = O N I

L I O H P

V 0 . - 1 0 P E O = S N L I A

N I P P M A L R C

N

P E I D M O

_ 5 V D D A V

. R E

F I L T O W N

R U Y O N G E S D I R O S R O S T S E I R

ꢀ 0 H T I W 8 0 4 L - 1 0 4 L E T A L P U P O

_ A C H

F µ 0 1 0 8 .

ꢀ 4 2 7

R 4 1

4 2 C 0

6

2 N L O

8

M M C O

2 H V O

2 L V O

1 7

1 8

1 9

V P S 2

7

_ 5 V D D A V

2 H I N

6

_ A C H

_ B C H

N C

2 0

2 D L M

5

1 D L M

4

V P S V

1 L V O

_ 5 V D D A V

2 1

2 2

1 H I N

3

1 H V O

M M C O

2 3

2 4

V P S 1

_ 5 V D D A V

2

1 N L O

1

_ B C H

)

E R W E L P B O S I A D = V 1 – ( 0

B L A N E N W R E D W O O P

E

V

D D _ 5 A V

V . 0 1 - 0 = G N E A R I N

L O G A

V . 0 5 - V 5 2 . 2 = G N E A R I N G I H A

N I P O L H I

B

A A N S D L E A N N R O C H F T U I R C C E I V R D I A G V L N A O I T P O

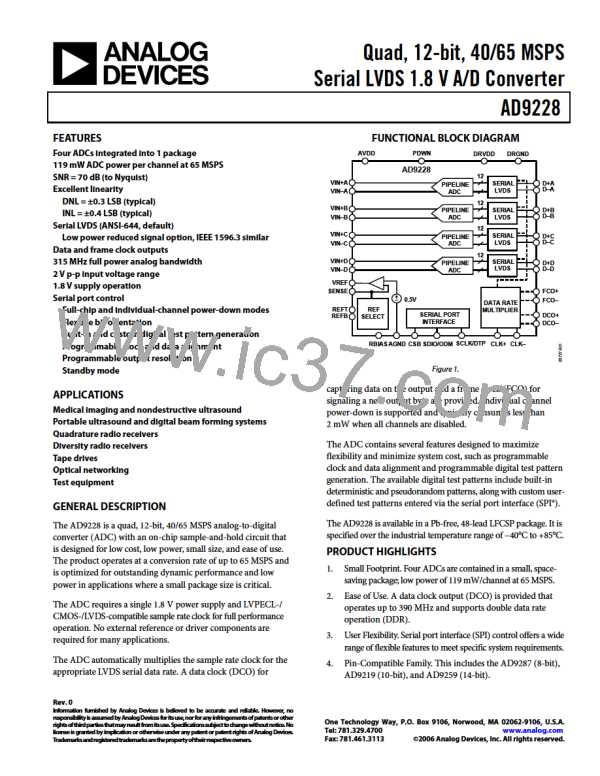

Figure 75. Evaluation Board Schematic, Optional DUT Analog Input Drive and SPI Interface (Continued)

Rev. 0 | Page ꢁ1 of 52

ADI [ ADI ]

ADI [ ADI ]