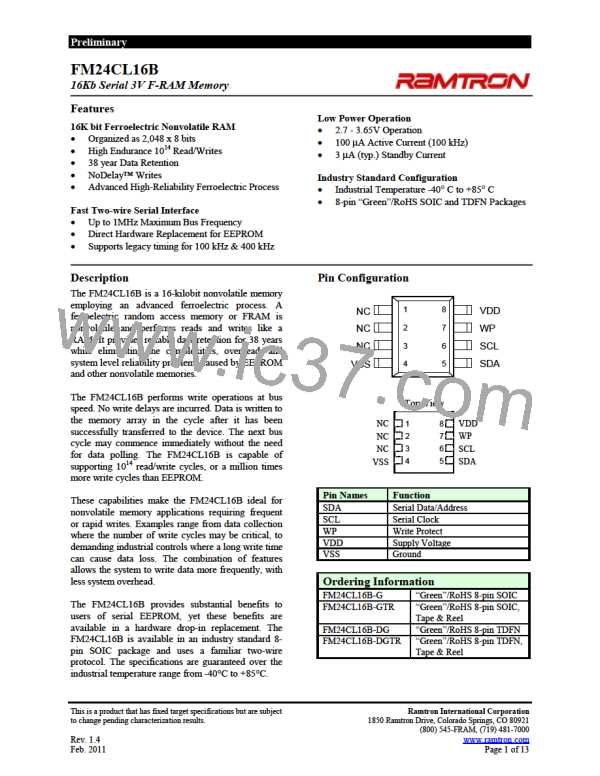

FM24CL16B - 16Kb 3V I2C F-RAM

SCL

SDA

7

6

0

Stop

Start

Data bits

(Transmitter)

Data bit Acknowledge

(Transmitter) (Receiver)

(Master) (Master)

Figure 3. Data Transfer Protocol

The receiver would fail to acknowledge for two

distinct reasons. First is that a byte transfer fails. In

this case, the No-Acknowledge ends the current

operation so that the part can be addressed again.

This allows the last byte to be recovered in the event

of a communication error.

Stop Condition

A stop condition is indicated when the bus master

drives SDA from low to high while the SCL signal is

high. All operations using the FM24CL16B must end

with a Stop condition. If an operation is pending

when a Stop is asserted, the operation will be aborted.

The master must have control of SDA (not a memory

read) in order to assert a Stop condition.

Second and most common, the receiver does not

acknowledge to deliberately end an operation. For

example, during a read operation, the FM24CL16B

will continue to place data onto the bus as long as

the receiver sends Acknowledges (and clocks).

When a read operation is complete and no more data

is needed, the receiver must not acknowledge the

last byte. If the receiver acknowledges the last byte,

this will cause the FM24CL16B to attempt to drive

the bus on the next clock while the master is sending

a new command such as a Stop.

Start Condition

A Start condition is indicated when the bus master

drives SDA from high to low while the SCL signal is

high. All read and write transactions begin with a

Start condition. An operation in progress can be

aborted by asserting a Start condition at any time.

Aborting an operation using the Start condition will

prepare the FM24CL16B for a new operation.

If during operation the power supply drops below the

specified VDD minimum, the system should issue a

Start condition prior to performing another operation.

Slave Address

The first byte that the FM24CL16B expects after a

Start condition is the slave address. As shown in

Figure 4, the slave address contains the device type,

the page of memory to be accessed, and a bit that

specifies if the transaction is a read or a write.

Data/Address Transfer

All data transfers (including addresses) take place

while the SCL signal is high. Except under the two

conditions described above, the SDA signal should

not change while SCL is high. For system design

considerations, keeping SCL in a low state while idle

improves robustness.

Bits 7-4 are the device type and should be set to

1010b for the FM24CL16B. The device type allows

other types of functions to reside on the 2-wire bus

within an identical address range. Bits 3-1 are used

for page select. They specify the 256-byte block of

memory that is targeted for the current operation. Bit

0 is the read/write bit. R/W=1 indicates a read

operation and R/W=0 indicates a write operation.

Acknowledge

The Acknowledge takes place after the 8th data bit has

been transferred in any transaction. During this state,

the transmitter should release the SDA bus to allow

the receiver to drive it. The receiver drives the SDA

signal low to acknowledge receipt of the byte. If the

receiver does not drive SDA low, the condition is a

No-Acknowledge and the operation is aborted.

Rev. 1.4

Feb. 2011

Page 4 of 13

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]