SigmaTel, Inc.

Data Sheet

STAC9721

9.7 ATE Test Mode

. ATE Test Mode

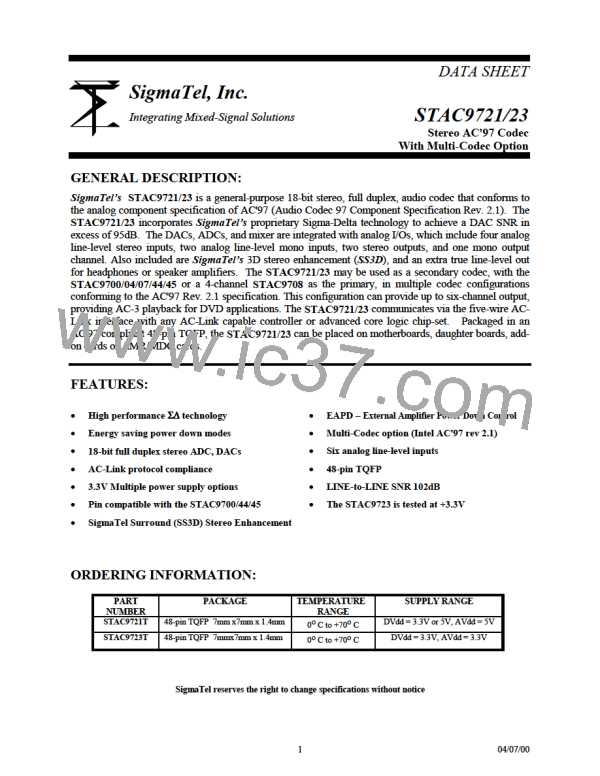

Figure 19

RESET#

SDATA_OUT

Tsetup2rst

Hi-Z

SDATA_IN, BIT_CLK

Toff

. ATE Test Mode

Table 29

Parameter

Symbol

Min

Typ

Max

Units

Setup to trailing edge of RESET#

(also applies to SYNC)

ToffTsetup2rst

15.0

-

-

ns

Setup to trailing edge of RESET#

(also applies to SYNC)

Tsetup2rst

Toff

15.0

-

-

-

-

ns

ns

Rising edge of RESET# to Hi-Z delay

25.0

1N.otesA:ll AC-Link signals are normally low through the trailing edge of RESET#. Bringing SDATA_OUT high for the

trailing edge of RESET# causes STAC9721/23’s AC-Link outputs to go high impedance which is suitable for

ATE in circuit testing.

2. Once either of the two test modes have been entered, the STAC9721/23 must be issued another RESET# with all

AC-Link signals low to return to the normal operating mode.

# denotes active low.

37

04/07/00

04/07/00

ETC [ ETC ]

ETC [ ETC ]