Data Sheet

June 1999

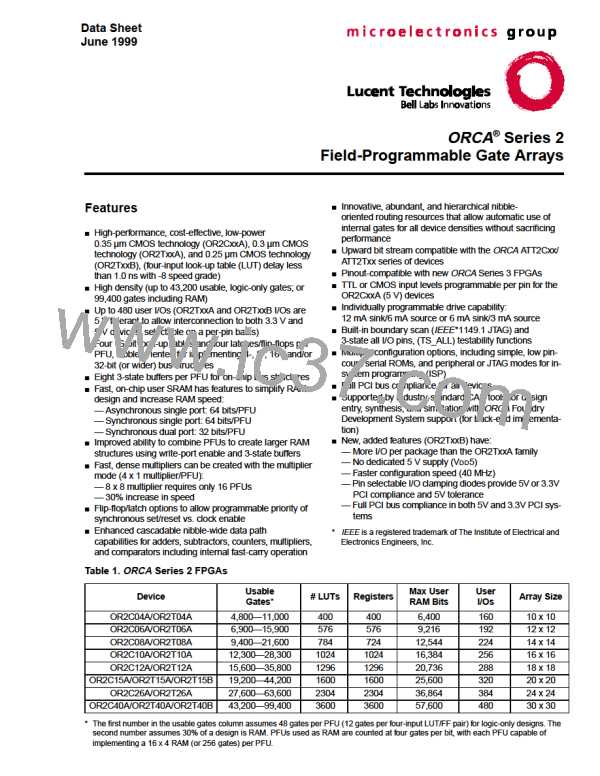

ORCA Series 2 FPGAs

G

I

Index

GSR (see GSRN)

GSRN, 6, 7, 16, 37, 134

A

Absolute Maximum Ratings, 129

Adder (see LUT Operating Modes)

Architecture

IEEE Standard 1149.1, 1

(see also Boundary Scan)

Overview, 5

Initialization (see FPGA States of Operation)

Input/Output Buffers (see PICs)

PLC, 22

PIC, 25

Measurement Conditions, 169

Output Buffer Characteristics, 170—172

B

Bidirectional Buffers (BIDIs), 14, 17, 18, 20, 22

(see also Routing and SLIC)

Bit Stream (see FPGA Configuration)

Bit Stream Error Checking, 47

(see also FPGA States of Operation)

Boundary Scan, 54—59

J

JTAG (see Boundary Scan)

L

Look-up Table (LUT) Operating Modes, 7—15

Adder-Subtractor Submode, 10

Counter Submode, 11

C

Equality Comparators, 11

Logic Modes, 7—9

Clock Distribution Network, 37—39

Selecting Clock Input Pins, 39

Memory Mode, 12—15

Asynchronous Memory, 12

Synchronous Memory, 13

Multiplier Submode, 11

Ripple Mode, 10

Clock Enable (CE), 1, 5, 7, 15, 16, 24, 134

Comparator (see LUT Operating Modes)

Configuration (see FPGA States of Operation

or FPGA Configuration)

Control Inputs, 5, 7

LSR, 5—7, 15—16

E

M

Electrical Characteristics, 130

Maximum Ratings (see Absolute Maximum Ratings)

Multiplier (see LUT Operating Modes)

Error Checking (see FPGA Configuration)

F

O

5 V Tolerant I/O, 26—27, 64

FPGA Configuration

ORCA Foundry Development System Overview, 4

Ordering Information, 189

Package Matrix, 190

Configuration Frame Format, 43—46

Configuration Modes, 47, 158—160

Asynchronous Peripheral Mode, 49, 163

Daisy-Chaining, 51

Package Options, 189

Temperature Options, 189

Voltage Options, 189

Master Parallel Mode, 47

Output (see PICs)

Master Serial Mode, 162

Slave Parallel Mode, 48, 50, 161, 166

Slave Serial Mode, 49—50, 165

Synchronous Peripheral Mode, 48, 164

Data Format, 43—45

P

Package Outline Drawings, 174—186

Package Matrix, 190

Using ORCA Foundry to Generate RAM Data, 43

FPGA States of Operation, 40—43

Configuration, 41

Package Outline Drawings, 173

84-Pin PLCC, 174

100-Pin TQFP, 175

Initialization, 40

144-Pin TQFP, 176

Other Configuration Options, 43

Partial Reconfiguration, 43

Reconfiguration, 42

Start-Up, 41

189

Lucent Technologies Inc.

ETC [ ETC ]

ETC [ ETC ]