Data Sheet

June 1999

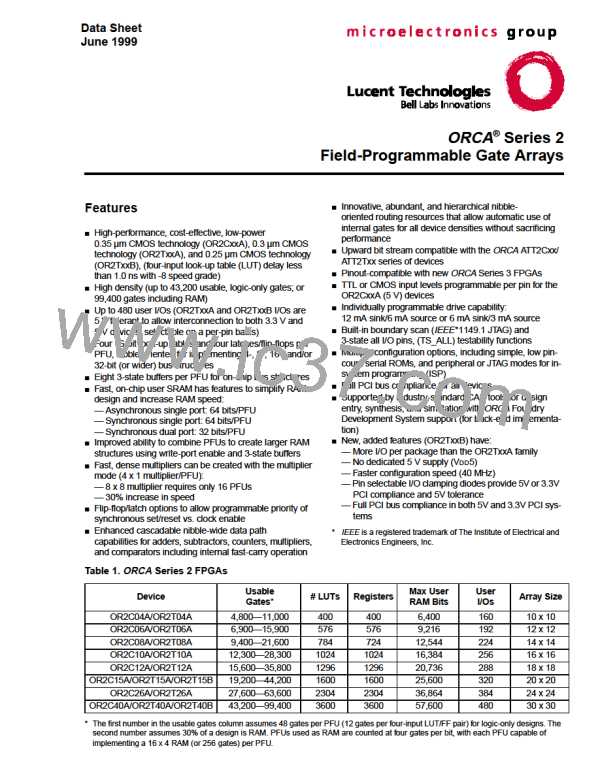

ORCA Series 2 FPGAs

Timing Characteristics (continued)

XSW LINES

FDBK_DEL

OUTPUT MUX

PFU

F[3:0]

4

F4*_DEL

A[4:0], B[4:0]

(LUT)

F3, F0

F1

2

2

F5*_DEL

A[4:0], B[4:0]

(LUT)

O[4:0]

MUX_DEL

C

XOR_DEL

ND_DEL

A[4:0], B[4:0]

(LUT)

F2

C0MUX_DEL, C0XOR_DEL, C0ND_DEL

C0

5-4633(F).a

C = controlled by configuration RAM.

Notes:

The parameters MUX_DEL, XOR_DEL, and ND_DEL include the delay through the LUT in F5A/F5B modes.

See Table 41 for an explanation of FDBK_DEL and OMUX_DEL.

Figure 54. Combinatorial PFU Timing

Lucent Technologies Inc.

133

ETC [ ETC ]

ETC [ ETC ]