NT5DS32M4AT

NT5DS16M8AT

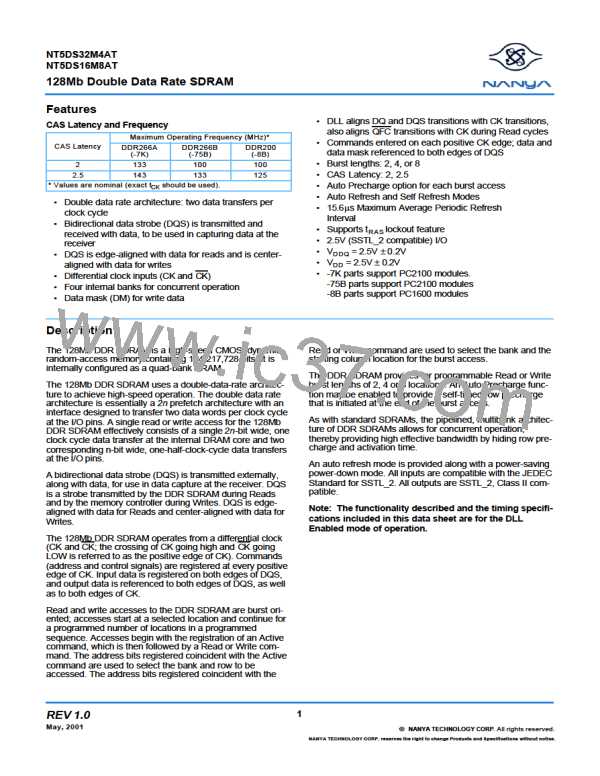

128Mb Double Data Rate SDRAM

Operations

Bank/Row Activation

Before any Read or Write commands can be issued to a bank within the DDR SDRAM, a row in that bank must be “opened”

(activated). This is accomplished via the Active command and addresses A0-A11, BA0 and BA1 (see Activating a Specific Row

in a Specific Bank), which decode and select both the bank and the row to be activated. After opening a row (issuing an Active

command), a Read or Write command may be issued to that row, subject to the tRCD specification. A subsequent Active com-

mand to a different row in the same bank can only be issued after the previous active row has been “closed” (precharged). The

minimum time interval between successive Active commands to the same bank is defined by tRC. A subsequent Active com-

mand to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access

overhead. The minimum time interval between successive Active commands to different banks is defined by tRRD

.

Activating a Specific Row in a Specific Bank

CK

CK

HIGH

CKE

CS

RAS

CAS

WE

RA = row address.

BA = bank address.

RA

BA

A0-A11

BA0, BA1

Don’ t Care

18

REV 1.0

May, 2001

©

NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

ETC [ ETC ]

ETC [ ETC ]