Pre-Production

WM8976

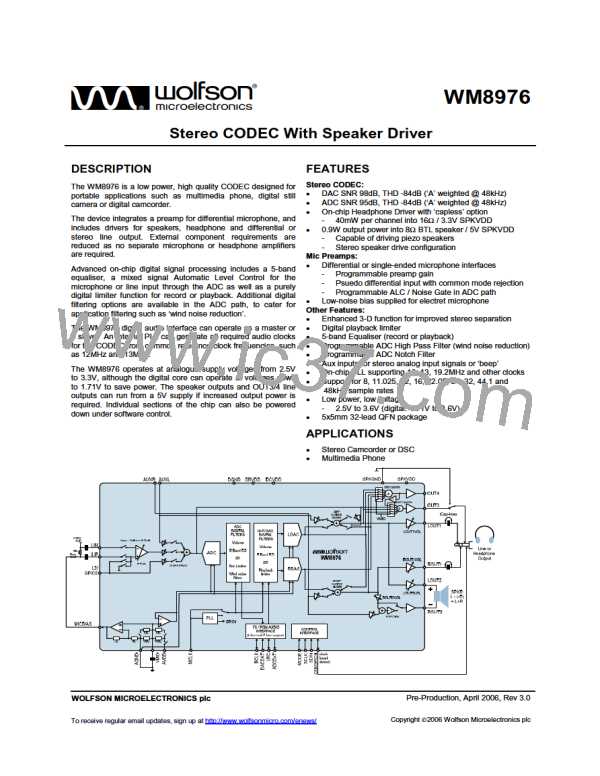

SIGNAL TIMING REQUIREMENTS

SYSTEM CLOCK TIMING

tMCLKL

MCLK

tMCLKH

tMCLKY

Figure 2 System Clock Timing Requirements

Test Conditions

DCVDD=1.8V, DBVDD=AVDD=SPKVDD=3.3V, DGND=AGND=SPKGND=0V, TA = +25oC

PARAMETER

SYMBOL

TMCLKY

CONDITIONS

MIN

TYP

MAX

UNIT

System Clock Timing Information

MCLK=SYSCLK (=256fs)

MCLK input to PLL Note 1

81.38

20

ns

ns

MCLK cycle time

MCLK duty cycle

TMCLKDS

60:40

40:60

Note 1:

PLL pre-scaling and PLL N and K values should be set appropriately so that SYSCLK is no greater than 12.288MHz.

AUDIO INTERFACE TIMING – MASTER MODE

Figure 3 Digital Audio Data Timing – Master Mode (see Control Interface)

PP Rev 3.0 April 2006

15

w

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]