T E C H N I C A L I N F O R M A T I O N

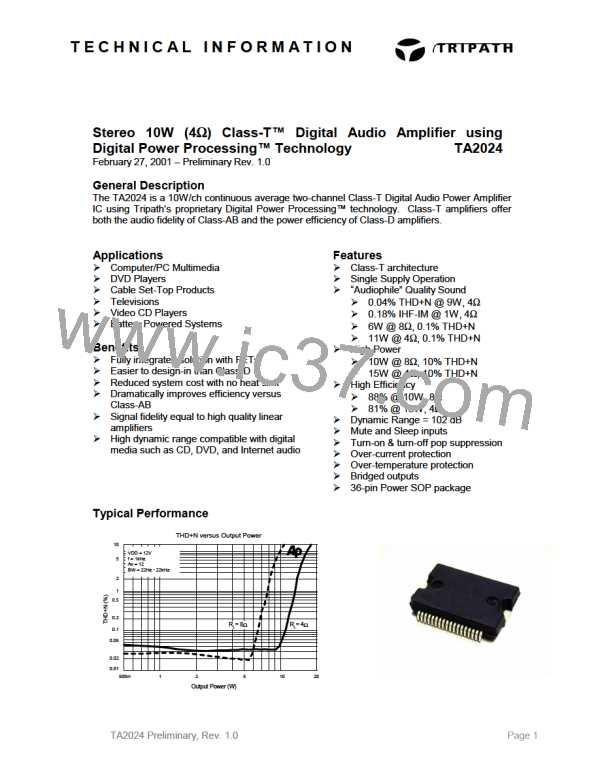

Application / Test Circuit

TA2024

VDD1

10

VP1

RF

20K

Lo

Ω

CI

10uH, 2A

OUTP1

DO

2.2uF

+

31

IN1 11

RI

20K

Ω

CZ

(Pin 35)

Processing

&

*Co

PGND1

VDD1

0.47uF

0.47uF

(Pin 35)

CA

0.1uF

CCM

Modulation

0.1uF

RL

BIASCAP 16

Lo

4

Ω

or *8

Ω

RZ

*Co

10uH, 2A

(Pin 8)

10 1/2W

Ω,

OUTM1

28

0.47uF

5V

5V

DO

(Pin 35)

MUTE

12

PGND1

19

FAULT

OVERLOADB

7

14

VP2

VDD2

RF

20K

CI

Ω

Lo

2.2uF

+

10uH, 2A

IN2 15

OUTP2

24

RI

20K

Ω

DO

CZ

*Co

6

(Pin 20)

Processing

&

REF

0.47uF

0.47uF

PGND2

VDD2

(Pin 20)

RREF

(Pin 8)

C

8.25K , 1%

Ω

Modulation

0.C1MuF

Lo

RL

RZ

3

*Co

DCAP1

10uH, 2A

4

Ω

or *8

Ω

OUTM2

10Ω, 1/2W

27

0.47uF

+12V

1meg

CD

DO

(Pin 20)

2

0.1uF

DCAP2

SLEEP

PGND2

Ω

18

36

33

22

1

CPUMP

0.1uF

+

CP

4

5V

1uF

CS

V5D

VDDA

DGND

CS

0.1uF

5

9

0.1uF

AGND1

V5A

CS

To Pin 1

0.1uF

+5VGEN

CS

To Pins 4,9

0.1uF

8

AGND2

AGND3

30

29

VDD1

VDD1

17

VDD (+12V)

+

CSW

CSW

0.1uF

35

PGND1

180uF, 16V

13

21

23

32

34

25

26

VDD2

VDD2

NC

+

CSW

CSW

180uF, 16V

0.1uF

20

PGND2

Note: Analog and Digital/Power Grounds must

be connected locally at the TA2024

Analog Ground

Digital/Power Ground

All Diodes Motorola MBRS130T3

* Use Co = 0.22µF for 8 Ohm loads

TA2024 Preliminary, Rev. 1.0

Page 5

TRIPATH [ TRIPATH TECHNOLOGY INC. ]

TRIPATH [ TRIPATH TECHNOLOGY INC. ]