TMC5130A DATASHEET (Rev. 1.14 / 2017-MAY-15)

25

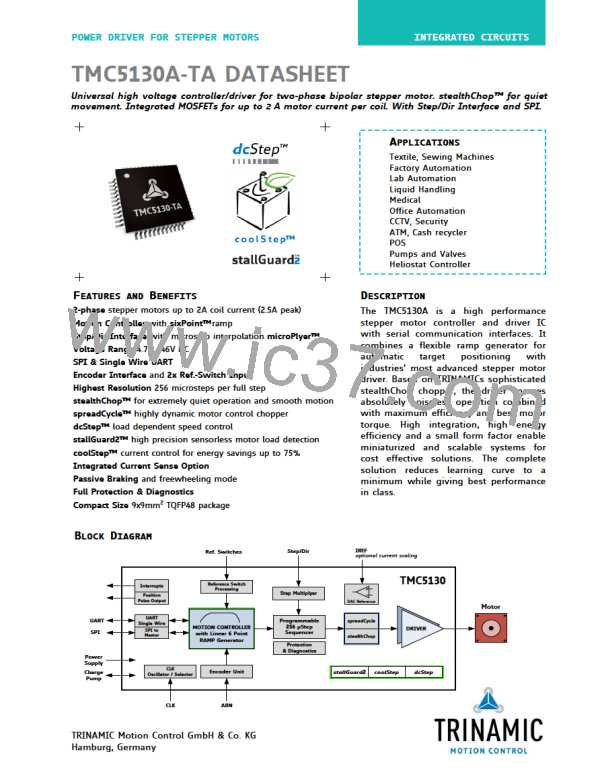

5.1.2 Read Access

UART READ ACCESS REQUEST DATAGRAM STRUCTURE

each byte is LSB…MSB, highest byte transmitted first

RW + 7 bit register

sync + reserved

8 bit slave address

8…15

CRC

24…31

CRC

address

16…23

0...7

Reserved (don’t cares

but included in CRC)

1

0

1

0

SLAVEADDR

register address

0

The read access request datagram structure is identical to the write access datagram structure, but

uses a lower number of user bits. Its function is the addressing of the slave and the transmission of

the desired register address for the read access. The TMC5130A responds with the same baud rate as

the master uses for the read request.

In order to ensure a clean bus transition from the master to the slave, the TMC5130A does not

immediately send the reply to a read access, but it uses a programmable delay time after which the

first reply byte becomes sent following a read request. This delay time can be set in multiples of

eight bit times using SENDDELAY time setting (default=8 bit times) according to the needs of the

master. In a multi-slave system, set SENDDELAY to min. 2 for all slaves. Otherwise a non-addressed

slave might detect a transmission error upon read access to a different slave.

UART READ ACCESS REPLY DATAGRAM STRUCTURE

each byte is LSB…MSB, highest byte transmitted first

0 ...... 63

8 bit slave

address

8…15

RW + 7 bit

register addr.

16…23

sync + reserved

32 bit data

CRC

56…63

CRC

0…7

24…55

data bytes 3, 2, 1, 0

(high to low byte)

register

1

0

1

0

reserved (0)

0xFF

0

address

The read response is sent to the master using address code %1111. The transmitter becomes switched

inactive four bit times after the last bit is sent.

Address %11111111 is reserved for read accesses going to the master. A slave cannot use this

address.

ERRATA IN READ ACCESS

A known bug in the UART interface implementation affects read access to registers that change during

the access. While the SPI interface takes a snapshot of the read register before transmission, the UART

interface transfers the register directly MSB to LSB without taking a snapshot. This may lead to

inconsistent data when reading out a register that changes during the transmission. Further, the CRC

sent from the driver may be incorrect in this case (but must not), which will lead to the master

repeating the read access. As a workaround, it is advised not to read out quickly changing registers

like XACTUAL, MSCNT or X_ENC during a motion, but instead first stop the motor or check the

position_reached flag to become active, and read out these values afterwards. If possible, use

X_LATCH and ENC_LATCH for a safe readout during motion (e.g. for homing). As the encoder cannot be

guaranteed to stand still during motor stop, only a dual read access and check for identical result

ensures correct X_ENC read data. Use the vzero and velocity_reached flag rather than reading VACTUAL.

www.trinamic.com

TRINAMIC [ TRINAMIC MOTION CONTROL GMBH & CO. KG. ]

TRINAMIC [ TRINAMIC MOTION CONTROL GMBH & CO. KG. ]