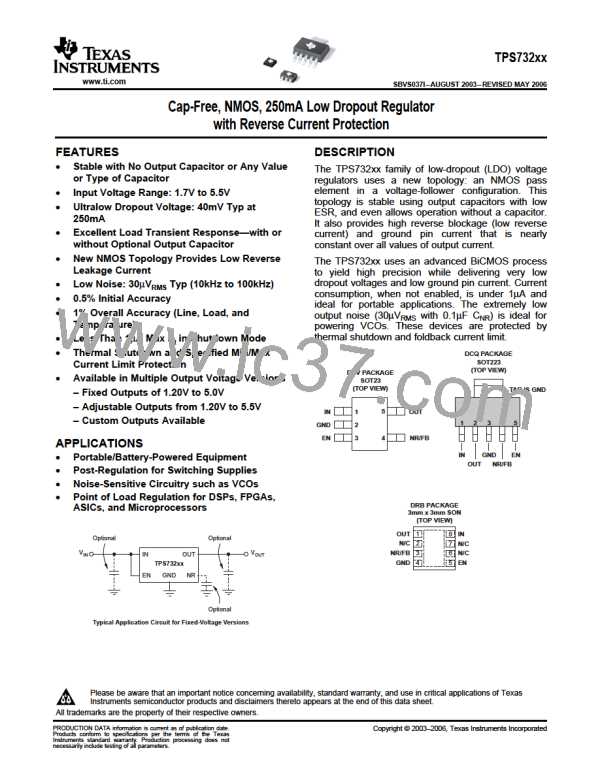

TPS732xx

www.ti.com

SBVS037I–AUGUST 2003–REVISED MAY 2006

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be

more susceptible to damage because very small parametric changes could cause the device not to meet its published

specifications.

ORDERING INFORMATION(1)

(2)

PRODUCT

VOUT

TPS732xxyyyz

XX is nominal output voltage (for example, 25 = 2.5V, 01 = Adjustable(3)).

YYY is package designator.

Z is package quantity.

(1) For the most current specification and package information, refer to the Package Option Addendum located at the end of this datasheet

or see the TI website at www.ti.com.

(2) Output voltages from 1.2V to 4.5V in 50mV increments are available through the use of innovative factory EEPROM programming;

minimum order quantities may apply. Contact factory for details and availability.

(3) For fixed 1.2V operation, tie FB to OUT.

ABSOLUTE MAXIMUM RATINGS

over operating junction temperature range unless otherwise noted(1)

TPS732xx

–0.3 to 6.0

–0.3 to 6.0

–0.3 to 5.5

–0.3 to 6.0

Internally limited

Indefinite

UNIT

VIN range

V

V

V

V

VEN range

VOUT range

VNR, VFB range

Peak output current

Output short-circuit duration

Continuous total power dissipation

Junction temperature range, TJ

Storage temperature range

ESD rating, HBM

See Dissipation Ratings Table

–55 to +150

–65 to +150

2

°C

°C

kV

V

ESD rating, CDM

500

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under the Electrical Characteristics

is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

POWER DISSIPATION RATINGS(1)

DERATING FACTOR

ABOVE TA = 25°C

T

A ≤ 25°C

TA = 70°C

TA = 85°C

BOARD

PACKAGE

RΘJC

RΘJA

POWER RATING POWER RATING POWER RATING

Low-K(2)

DBV

DBV

DCQ

DRB

64°C/W

64°C/W

15°C/W

1.2°C/W

255°C/W

180°C/W

53°C/W

40°C/W

3.9mW/°C

5.6mW/°C

18.9mW/°C

25.0mW/°C

390mW

560mW

1.89W

2.50W

215mW

310mW

1.04W

1.38W

155mW

225mW

0.76W

1.0W

(3)

High-K

Low-K(2)

High-K(3)(4)

(1) See Power Dissipation in the Applications section for more information related to thermal design.

(2) The JEDEC Low-K (1s) board design used to derive this data was a 3 inch x 3 inch, two-layer board with 2-ounce copper traces on top

of the board.

(3) The JEDEC High-K (2s2p) board design used to derive this data was a 3 inch x 3 inch, multilayer board with 1-ounce internal power and

ground planes and 2-ounce copper traces on the top and bottom of the board.

(4) Based on preliminary thermal simulations.

2

Submit Documentation Feedback

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]