TPS3808-Q1

www.ti.com

SBVS085H –JANUARY 2007–REVISED JUNE 2012

3.3V

V

SENSE

DD

Ω

90k

CT

TPS3808xxx

GND

Figure 11. Using an External MOSFET to Minimize IDD When MR Signal Does Not Go to VDD

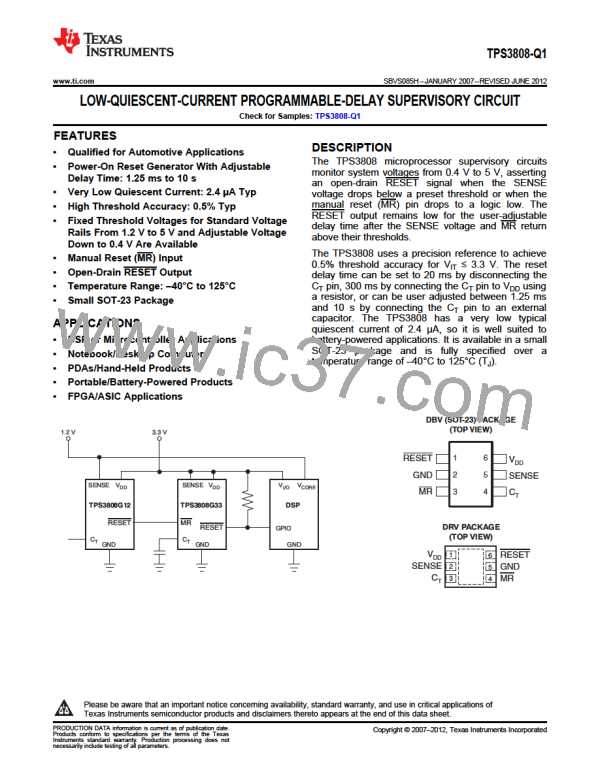

Selecting the Reset Delay Time

The TPS3808 has three options for setting the RESET delay time as shown in Figure 12. Figure 12a shows the

configuration for a fixed 300-ms typical delay time by tying CT to VDD; a resistor from 40 kΩ to 200 kΩ must be

used. Supply current is not affected by the choice of resistor. Figure 12b shows a fixed 20-ms delay time by

leaving the CT pin open. Figure 12c shows a ground referenced capacitor connected to CT for a user-defined

program time between 1.25 ms and 10 s.

The capacitor CT should be ≥100 pF nominal value in order for the TPS3808 to recognize that the capacitor is

present. The capacitor value for a given delay time can be calculated using the following equation:

*3

ƪ

ƫ

CT (nF) + tD (s)*0.5 10 (s) 175

(1)

The reset delay time is determined by the time it takes an on-chip precision 220-nA current source to charge the

external capacitor to 1.23 V. When a RESET is asserted, the capacitor is discharged. When the RESET

conditions are cleared, the internal current source is enabled and begins to charge the external capacitor. When

the voltage on this capacitor reaches 1.23 V, RESET is deasserted. Note that a low-leakage type capacitor such

as a ceramic should be used and that stray capacitance around this pin may cause errors in the reset delay time.

Immunity to SENSE Pin Voltage Transients

The TPS3808 is relatively immune to short negative transients on the SENSE pin. Sensitivity to transients is

dependent on threshold overdrive, as shown in the Maximum Transient Duration at Sense vs Sense Threshold

Overdrive Voltage graph (Figure 5) in the Typical Characteristics section.

3.3V

3.3V

3.3V

SENSE VDD

SENSE VDD

SENSE VDD

Ω

50k

TPS3808G33

TPS3808G33

TPS3808G33

RESET

CT RESET

CT RESET

CT

CT

−3

Delay (s) = C (nF) + 0.5 x 10 (s)

T

300ms Delay

20ms Delay

175

(b)

(a)

(c)

Figure 12. Configuration Used to Set the RESET Delay Time

Copyright © 2007–2012, Texas Instruments Incorporated

9

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]