LMQ62440-Q1

ZHCSM24A –MARCH 2020 –REVISED SEPTEMBER 2020

www.ti.com.cn

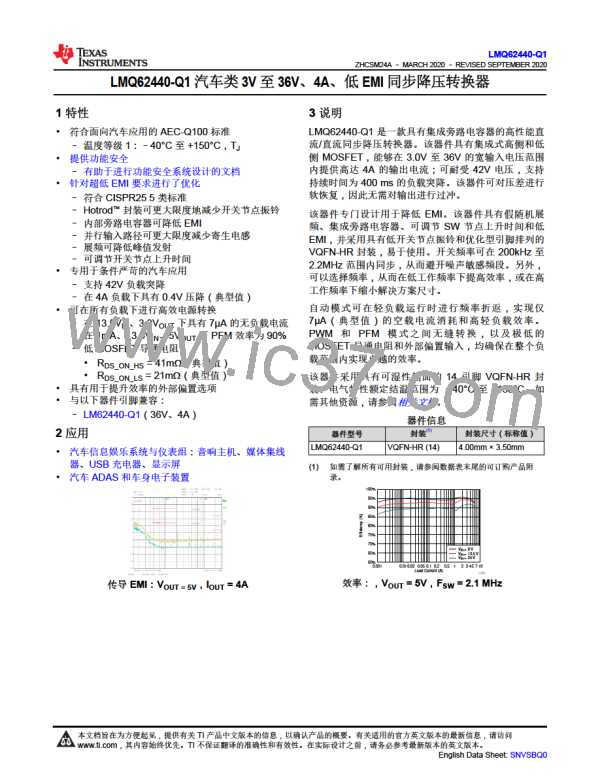

6 引脚配置和功能

PGND2

11

BIAS

1

VCC

AGND

FB

2

3

4

SW

10

5

9

PGOOD

PGND1

图6-1. RJR 封装14 引脚VQFN-HR 顶视图

引脚功能

引脚

I/O

说明

名称

编号

内部LDO 输入。连接到输出电压点以提高效率。将一个可选的优质0.1µF 至1µF 电容器从该引脚接地,以

提高抗噪性。如果输出电压高于12V,则将该引脚接地。

BIAS

1

P

内部LDO 输出。用作内部控制电路的电源。不要连接至任何外部负载。在该引脚和AGND 之间连接一个

1µF 优质电容器。

VCC

2

O

内部电路的模拟地。反馈和VCC 是相对于该引脚测量的。必须将AGND 连接到PCB 上的PGND1 和

PGND2。

AGND

FB

3

4

5

G

I

内部控制环路的输出电压反馈输入。连接到反馈分压器抽头点以实现可调输出电压。请勿悬空或接地。

开漏电源正常状态输出。通过限流电阻器将该引脚上拉至合适的电压电源。高电平= 电源正常,低电平= 故

障。当EN = 低电平且VIN > 1V 时,PGOOD 输出变为低电平。如果不使用,它可以保持开路或接地。

PGOOD

O

MODE/

SYNC

该引脚控制LMQ62440-Q1 的运行模式。模式包括自动模式(自动PFM/PWM 运行)、FPWM 以及与外部时

钟的同步。同步后,时钟在外部时钟的上升沿触发。此外,展频运行由该引脚控制。请勿将该引脚悬空。

6

I

精密使能输入。高电平= 开启,低电平= 关闭。可连接至VIN。精密使能允许将该引脚用作可调节UVLO。

请参阅节9

EN

7

8

I

VIN1

PGND1

SW

P

G

O

G

转换器的输入电源。将一个或多个优质旁路电容器从该引脚连接到PGND1。必须为VIN2 提供低阻抗连接。

内部低侧MOSFET 的电源地。连接到系统地。必须为PGND2 提供低阻抗连接。将一个或多个优质旁路电容

器从该引脚连接到VIN1。

9

10

11

转换器的开关节点。连接到输出电感器。

内部低侧MOSFET 的电源地。连接到系统地。必须为PGND1 提供低阻抗连接。将一个或多个优质旁路电容

器从该引脚连接到VIN2。

PGND2

VIN2

12

13

P

转换器的输入电源。将一个或多个优质旁路电容器从该引脚连接到PGND2。必须为VIN1 提供低阻抗连接。

通过一个电阻器连接到CBOOT。该电阻必须介于0Ω和开路之间,并决定SW 节点上升时间。

RBOOT

I/O

高侧驱动器上部电源轨。在SW 引脚和CBOOT 之间连接一个100nF 电容器。一个内部二极管连接到

VCC,并允许CBOOT 在SW 节点为低电平时充电。

CBOOT

14

I/O

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: LMQ62440-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]