CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

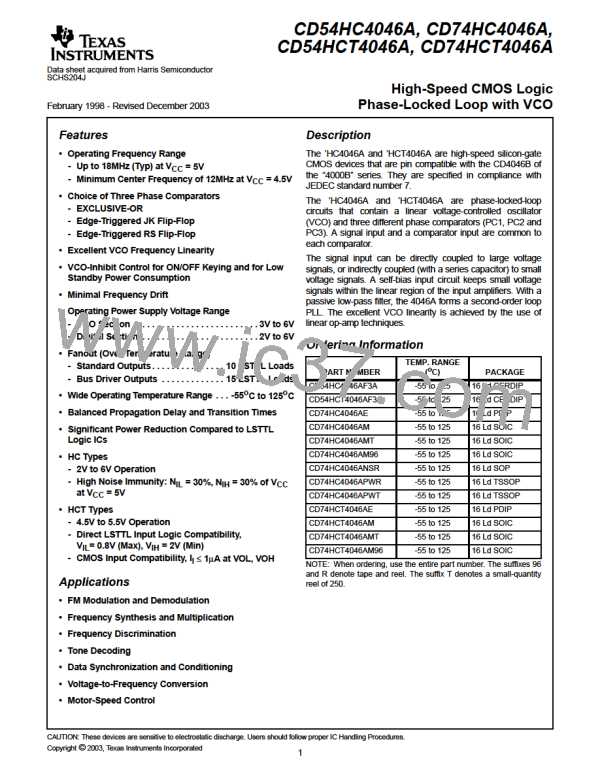

DC Electrical Specifications (Continued)

TEST

CONDITIONS

o

o

o

o

o

25 C

-40 C TO 85 C -55 C TO 125 C

V

CC

PARAMETER

SYMBOL

V (V)

I

I

(mA)

(V)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

UNITS

O

SIG , COMP

V

IL

-

-

4.5 to

5.5

-

-

0.8

-

0.8

-

0.8

V

IN

DC Coupled

IN

Low-Level Input

Voltage

PCP

High-Level Output

Voltage

CMOS Loads

, PCn OUT

V

V

V

V

V

or V

or V

or V

or V

-

-

-

-

-

4.5

4.5

4.5

4.5

5.5

4.4

-

-

-

-

-

-

4.4

-

4.4

3.7

-

-

V

V

OUT

OH

IL

IL

IL

IL

IH

IH

IH

IH

PCP

High-Level Output

Voltage

TTL Loads

, PCn OUT

V

3.98

-

3.84

-

-

OUT

OH

PCP

Low-Level Output

Voltage

CMOS Loads

, PCn OUT

V

-

-

-

0.1

0.26

±30

-

-

0.1

0.33

±38

0.1

0.4

±45

V

OUT

OL

PCP

Low-Level Output

Voltage

, PCn OUT

V

-

V

OUT

OL

TTL Loads

SIG , COMP Input

IN IN

I

Any

µA

I

Leakage Current

Voltage

Between

V

and

CC

GND

PC2

Three-State

Off-State Current

I

V

or V

IH

-

5.5

4.5

-

-

-

±0.5

±5

-

-

-

-

±10

µA

kΩ

OUT

OZ

IL

SIG , COMP Input

R

V at Self-Bias

250

-

-

-

IN

IN

I

I

Resistance

Operation Point:

∆V = 0.5V,

I

See Figure 10

DEMODULATOR SECTION

Resistor Range

R

at R > 300kΩ

Leakage Current

Can Influence

4.5

4.5

5

-

-

300

-

-

-

-

-

-

-

-

-

kΩ

S

S

V

DEM OUT

V = V =

VCO IN

Offset Voltage VCO

V

±20

mV

IN

OFF

I

V

to V

CC

2

DEM

Values taken over

Range

R

S

See Figure 23

Dynamic Output

Resistance at

R

V

=

4.5

5.5

-

25

-

-

-

-

-

Ω

D

DEM OUT

V

CC

2

DEM

OUT

Quiescent Device

Current

I

V

or

-

-

-

-

-

8

-

-

80

-

-

160

490

µA

µA

CC

CC

GND

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

∆I

V

4.5 to

5.5

100

360

450

CC

CC

-2.1

(Note 4)

Excluding

Pin 5

NOTES:

2. The value for R1 and R2 in parallel should exceed 2.7kΩ.

3. The maximum operating voltage can be as high as V -0.9V, however, this may result in an increased offset voltage.

CC

4. For dual-supply systems theoretical worst case (V = 2.4V, V

= 5.5V) specification is 1.8mA.

CC

I

9

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]