CC2640R2L

ZHCSRK4A –APRIL 2020 –REVISED SEPTEMBER 2020

www.ti.com.cn

9.6 Debug

The on-chip debug support is done through a dedicated cJTAG (IEEE 1149.7) or JTAG (IEEE 1149.1) interface.

9.7 Power Management

To minimize power consumption, the CC2640R2L MCU supports a number of power modes and power

management features (see 表9-1).

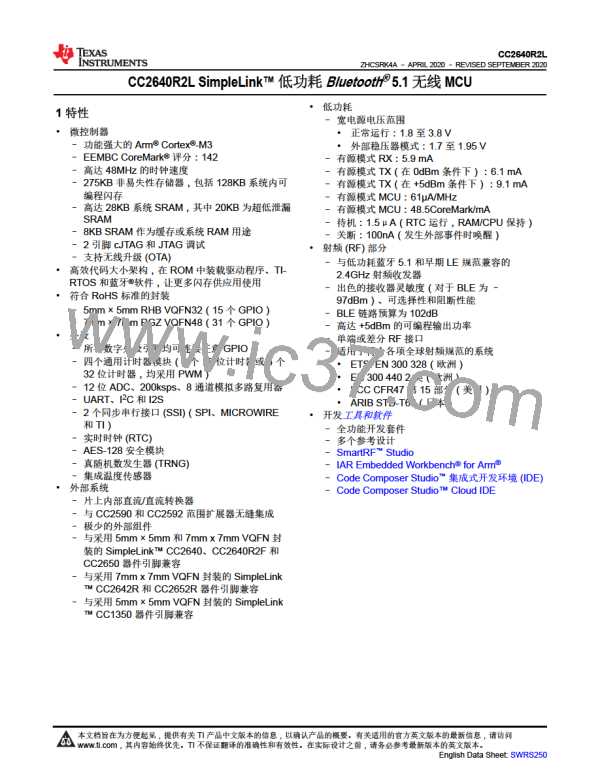

表9-1. Power Modes

SOFTWARE CONFIGURABLE POWER MODES

RESET PIN

HELD

MODE

ACTIVE

IDLE

Off

STANDBY

Off

SHUTDOWN

CPU

Active

Off

Off

Off

Off

Flash

On

Available

On

Off

SRAM

On

Available

On

Off

Off

Radio

Available

On

Off

Off

Off

Supply System

Current

On

Duty Cycled

1.5 µA

151 µs

Partial

Full

Off

Off

1.45 mA + 31 µA/MHz

650 µA

14 µs

Full

0.15 µA

1015 µs

No

0.1 µA

1015 µs

No

Wake-up Time to CPU Active(1)

Register Retention

SRAM Retention

–

Full

Full

Full

No

No

XOSC_HF or

RCOSC_HF

XOSC_HF or

RCOSC_HF

High-Speed Clock

Low-Speed Clock

Off

Off

Off

Off

Off

XOSC_LF or

RCOSC_LF

XOSC_LF or

RCOSC_LF

XOSC_LF or

RCOSC_LF

Peripherals

Available

Available

Available

Available

Active

Available

Available

Available

Available

Active

Off

Off

Off

Off

Off

Wake up on RTC

Available

Available

Available

Duty Cycled

Active

Wake up on Pin Edge

Wake up on Reset Pin

Brown Out Detector (BOD)

Power On Reset (POR)

Available

Available

Off

Off

Available

N/A

Active

Active

Active

N/A

(1) Not including RTOS overhead

In active mode, the application CM3 CPU is actively executing code. Active mode provides normal operation of

the processor and all of the peripherals that are currently enabled. The system clock can be any available clock

source (see 表9-1).

In idle mode, all active peripherals can be clocked, but the Application CPU core and memory are not clocked

and no code is executed. Any interrupt event will bring the processor back into active mode.

In standby mode, only the always-on domain (AON) is active. An external wake-up event or RTC event is

required to bring the device back to active mode. MCU peripherals with retention do not need to be reconfigured

when waking up again, and the CPU continues execution from where it went into standby mode. All GPIOs are

latched in standby mode.

In shutdown mode, the device is turned off entirely, including the AON domain. The I/Os are latched with the

value they had before entering shutdown mode. A change of state on any I/O pin defined as a wake-up from

Shutdown pin wakes up the device and functions as a reset trigger. The CPU can differentiate between a reset in

this way, a reset-by-reset pin, or a power-on-reset by reading the reset status register. The only state retained in

this mode is the latched I/O state and the Flash memory contents.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

31

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]