AM6548, AM6528, AM6526

ZHCSLA7B –DECEMBER 2019 –REVISED JUNE 2021

www.ti.com.cn

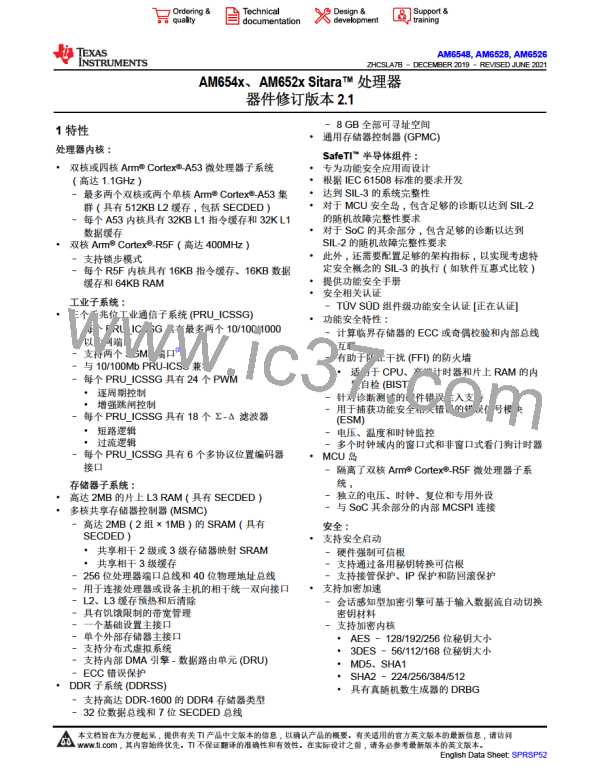

6.2 Pin Attributes

表6-1 describes the terminal characteristics and the signals multiplexed on each ball.

表6-1. Pin Attributes

BALL

RESET

REL.

RXACTIVE

BALL

RESET

I/O

VOLTAGE

PULL UP/

DOWN

TYPE [12]

BALL NUMBER

MUXMOD

E [4]

BUFFER

TYPE [11]

/

IO Daisy

BALL NAME [2]

SIGNAL NAME [3]

TYPE [5]

POWER [9]

HYS [10]

DSIS [13]

[1]

TXDISABL Chain [15]

E [14]

STATE [6] MUXMOD VALUE [8]

E [7]

P17

V17

W16

M14

L15

CAP_VDDAR_CORE0

CAP_VDDAR_CORE1

CAP_VDDAR_CORE2

CAP_VDDAR_CORE3

CAP_VDDAR_CORE4

CAP_VDDAR_MCU

CAP_VDDAR_CORE0

CAP

CAP_VDDAR_CORE1

CAP_VDDAR_CORE2

CAP_VDDAR_CORE3

CAP_VDDAR_CORE4

CAP_VDDAR_MCU

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

CAP

U10

M12

N12

N18

N15

Y10

AA8

CAP_VDDAR_MPU0_0

CAP_VDDAR_MPU0_1

CAP_VDDAR_MPU1_0

CAP_VDDAR_MPU1_1

CAP_VDDAR_WKUP

CAP_VDDAR_MPU0_0

CAP_VDDAR_MPU0_1

CAP_VDDAR_MPU1_0

CAP_VDDAR_MPU1_1

CAP_VDDAR_WKUP

CAP_VDDA_1P8_IOLDO_WK CAP_VDDA_1P8_IOLDO_WKUP

UP

J17

G19

Y19

H18

V9

CAP_VDDA_1P8_SDIO

CAP_VDDA_1P8_IOLDO0

CAP_VDDA_1P8_IOLDO1

CAP_VDDSHV_SDIO

CAP_VDD_WKUP

CAP_VDDA_1P8_SDIO

CAP_VDDA_1P8_IOLDO0

CAP_VDDA_1P8_IOLDO1

CAP_VDDSHV_SDIO

CAP_VDD_WKUP

CAP

CAP

CAP

CAP

CAP

I

G28

CSI0_RXN0

CSI0_RXN0

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

1.8 V

VDDA_1P8_C

SI0

DPHY

DPHY

DPHY

DPHY

DPHY

DPHY

DPHY

DPHY

DPHY

DPHY

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

No

No

No

No

No

No

No

No

No

No

H27

F26

H25

G24

F28

G27

G26

G25

F24

CSI0_RXN1

CSI0_RXN2

CSI0_RXN3

CSI0_RXN4

CSI0_RXP0

CSI0_RXP1

CSI0_RXP2

CSI0_RXP3

CSI0_RXP4

CSI0_RXN1

CSI0_RXN2

CSI0_RXN3

CSI0_RXN4

CSI0_RXP0

CSI0_RXP1

CSI0_RXP2

CSI0_RXP3

CSI0_RXP4

I

I

I

I

I

I

I

I

I

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

VDDA_1P8_C

SI0

Copyright © 2021 Texas Instruments Incorporated

12

Submit Document Feedback

Product Folder Links: AM6548 AM6528 AM6526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]