HV5522/HV5530/HV5622/HV5630

Functional Block Diagram

Polarity

Blanking

Latch Enable

HVOUT1

Data Input

Clock

Latch

Latch

HVOUT

2

32-Bit

Shift

Register

(Outputs 3 to 30

not shown)

HVOUT31

HVOUT32

Latch

Latch

Data Out

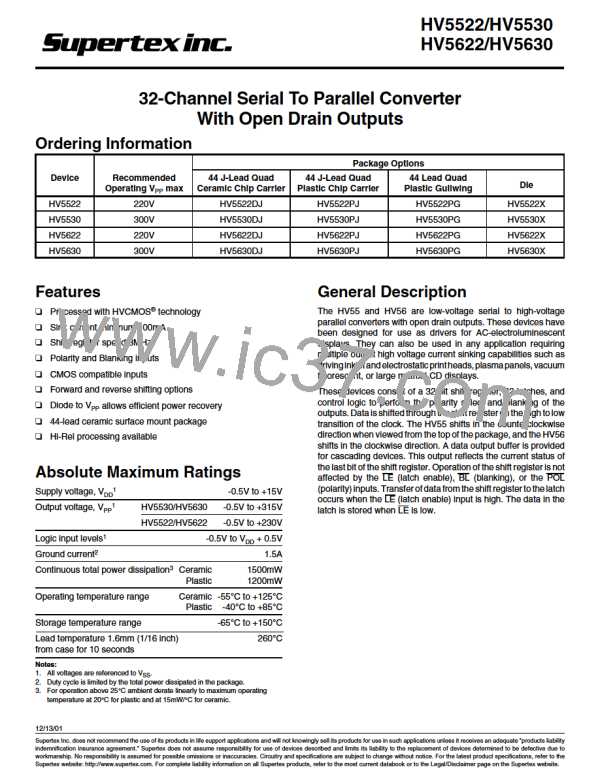

Function Table

Inputs

Outputs

HV Outputs

Function

Shift Reg

Data Out

Data

CLK

LE

BL

POL

1

2…32

*…*

1

2…32

*

All on

X

X

X

X

L

L

L

L

H

L

*

On

On…On

*

*

*

*

*

*

*

*

All off

X

X

*

*…*

Off Off…Off

Invert mode

Load S/R

X

X

H

H

H

H

H

H

*

*…*

*

*

*…*

*…*

*…*

*…*

*…*

*…*

H or L

↓

H or L

H or L

↓

L

H

H

L

H or L *…*

Load

Latches

X

X

L

↑

*

*

*…*

*…*

*…*

*…*

*

↑

*

Transparent

Latch mode

H

H

H

H

L

H

Off

On

H

↓

Notes:

H = high level, L = low level, X = irrelevant, ↓ = high-to-low transition, ↑ = low-to-high transistion.

* = dependent on previous stage’s state before the last CLK ↓ or last LE high.

4

SUPERTEX [ Supertex, Inc ]

SUPERTEX [ Supertex, Inc ]