7 Layout

VIPer50A-E/ASP-E

7

Layout

7.1

Layout Considerations

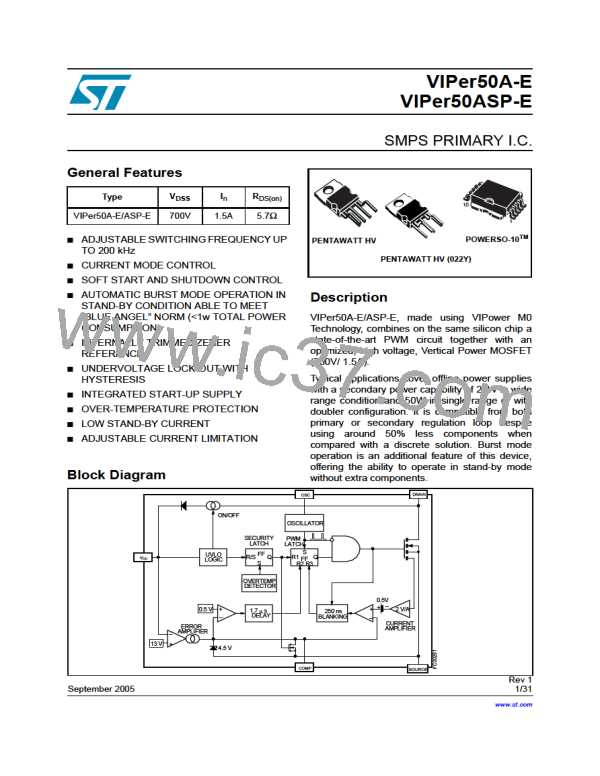

Some simple rules insure a correct running of switching power supplies. They may be

classified into two categories:

–

Minimizing power loops: The switched power current must be carefully analysed and

the corresponding paths must be as small an inner loop area as possible. This avoids

radiated EMC noises, conducted EMC noises by magnetic coupling, and provides a

better efficiency by eliminating parasitic inductances, especially on secondary side.

–

Using different tracks for low level and power signals: Interference due to mixing of

signal and power may result in instabilities and/or anomalous behavior of the device

in case of violent power surge (Input overvoltages, output short circuits...).

In case of VIPer, these rules apply as shown on (see Figure 24).

–

–

–

Loops C1-T1-U1, C5-D2-T1, and C7-D1-T1 must be minimized.

C6 must be as close as possible to T1.

Signal components C2, ISO1, C3, and C4 are using a dedicated track connected

directly to the power source of the device.

Figure 24. Recommended Layout

T1

D1

To secondary

filteringand load

C7

D2

R1

VDD

DRAIN

-

C1

C5

OSC

+

13V

From input

diodes bridge

COMP SOURCE

U1

VIPerXX0

R2

C4

C6

C2

C3

ISO1

FC00500

22/31

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]