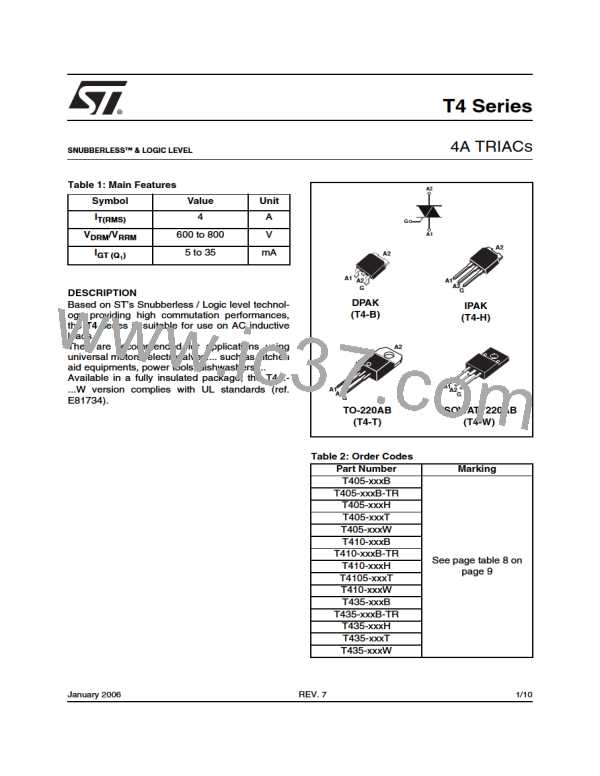

T4 Series

Figure 7: Non-repetitive surge peak on-state

current for a sinusoidal pulse with width tp < 10 ms

and corresponding value of I2t

Figure 8: Relative variation of gate trigger

current, holding current and latching current

versus junction temperature (typical values)

I

,I ,I [T ] / I ,I ,I [T =25°C]

H L j GT H L j

GT

I

(A), I2t (A2s)

TSM

2.5

2.0

1.5

1.0

0.5

0.0

500

100

Tj initial=25°C

dI/dt limitation:

50A/µs

IGT

ITSM

IH & IL

10

I2t

T (°C)

j

t (ms)

p

1

-40

-20

0

20

40

60

80

100

120

140

0.01

0.10

1.00

10.00

Figure 9: Relative variation of critical rate of

decrease of main current versus (dV/dt)c

(typical values)

Figure 10: Relative variation of critical rate of

decrease of main current versus junction

temperature

(dI/dt)c [T ] / (dI/dt)c [T specified]

j

j

(dI/dt)c [(dV/dt)c] / Specified (dI/dt)c

6

5

4

3

2

1

0

2.4

2.2

2.0

1.8

1.6

1.4

1.2

T435

1.0

0.8

T410

0.6

0.4

0.2

0.0

T405

(dV/dt)c (V/µs)

T (°C)

j

0.1

1.0

10.0

100.0

0

25

50

75

100

125

Figure 11: DPAK thermal resistance junction to

ambient versus copper surface under tab (printed

circuit board FR4, copper thickness: 35 µm)

R

(°C/W)

th(j-a)

100

90

80

70

60

50

40

30

20

10

0

S(cm²)

0

4

8

12

16

20

24

28

32

36

40

5/10

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]