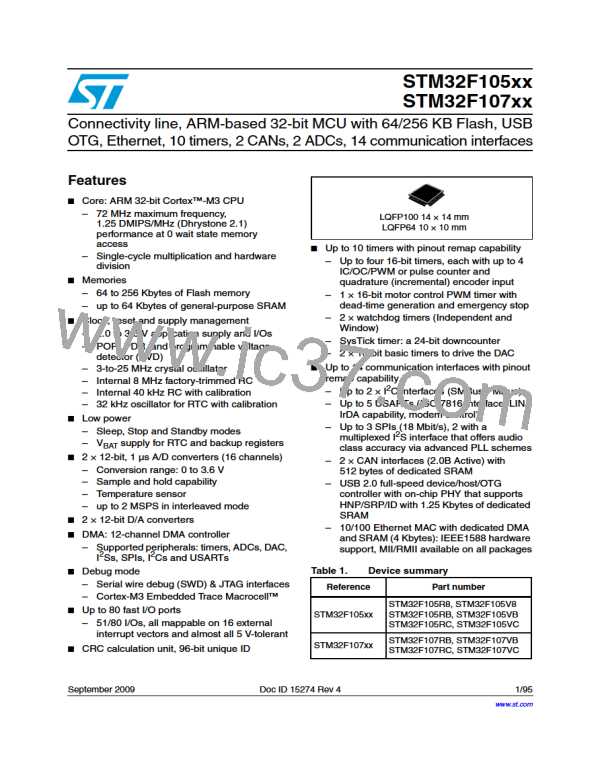

STM32F105xx, STM32F107xx

List of figures

List of figures

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

STM32F105xx and STM32F107xx connectivity line block diagram . . . . . . . . . . . . . . . . . 12

STM32F105xxx and STM32F107xxx connectivity line LQFP100 pinout . . . . . . . . . . . . . . 23

STM32F105xxx and STM32F107xxx connectivity line LQFP64 pinout . . . . . . . . . . . . . . . 24

Memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Typical current consumption on V

different V

with RTC on vs. temperature at

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

BAT

BAT

Figure 10. Typical current consumption in Stop mode with regulator in Run mode

versus temperature at different V values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

DD

Figure 11. Typical current consumption in Stop mode with regulator in Low-power

mode versus temperature at different V values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

DD

Figure 12. Typical current consumption in Standby mode versus temperature at

different V values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

DD

Figure 13. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 14. Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 15. Typical application with an 8 MHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 16. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 17. I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 18. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2

Figure 19. I C bus AC waveforms and measurement circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 20. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

(1)

Figure 21. SPI timing diagram - slave mode and CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

(1)

Figure 22. SPI timing diagram - master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

(1)

2

Figure 23. I S slave timing diagram (Philips protocol) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

2

(1)

Figure 24. I S master timing diagram (Philips protocol) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 25. USB OTG FS timings: definition of data signal rise and fall time . . . . . . . . . . . . . . . . . . . . 65

Figure 26. Ethernet SMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 27. Ethernet RMII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 28. Ethernet MII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 29. ADC accuracy characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 30. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 31. Power supply and reference decoupling (V

Figure 32. Power supply and reference decoupling (V

not connected to V

connected to V

). . . . . . . . . . . . . . 72

DDA

). . . . . . . . . . . . . . . . . 72

REF+

REF+

DDA

Figure 33. 12-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 34. LQFP100, 100-pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . . 77

(1)

Figure 35. Recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 36. LQFP64 – 64 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

(1)

Figure 37. Recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 38. LQFP100 P max vs. T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

D

A

Figure 39. USB OTG FS device mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 40. Host connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 41. OTG connection (any protocol). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 42. MII mode using a 25 MHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 43. RMII with a 50 MHz oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 44. RMII with a 25 MHz crystal and PHY with PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Doc ID 15274 Rev 4

7/95

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]