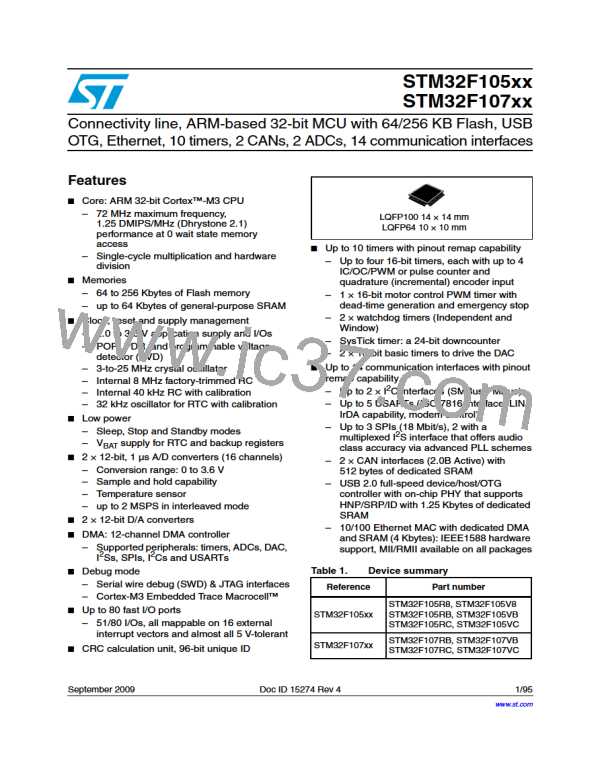

STM32F105xx, STM32F107xx

Description

2.2

Full compatibility throughout the family

The STM32F105xx and STM32F107xx constitute the connectivity line family whose

members are fully pin-to-pin, software and feature compatible.

The STM32F105xx and STM32F107xx are a drop-in replacement for the low-density

(STM32F103x4/6), medium-density (STM32F103x8/B) and high-density

(STM32F103xC/D/E) performance line devices, allowing the user to try different memory

densities and peripherals providing a greater degree of freedom during the development

cycle.

(1)

Table 3.

STM32F105xx and STM32F107xx family versus STM32F103xx family

STM32

Low-density

Medium-density

High-density

STM32F105xx

STM32F107xx

device STM32F103xx devices STM32F103xx devices

STM32F103xx devices

Flash

16

6

32

10

32

10

64

20

128

20

256

48

384

64

512

64

64

128 256

128

48

256

64

size (KB)

RAM

20

32

64

size (KB)

144 pins

100 pins

5 × USARTs,

4 × 16-bit timers,

2 × basic timers,

3 × SPIs,

5 × USARTs,

5 × USARTs

4 × 16-bit timers,

4 × 16-bit timers,

2 × basic timers,

3 × SPIs,

3 × USARTs

3 × 16-bit

timers

2 × basic timers, 3 × SPIs,

2 × I2Ss, 2 × I2Cs, USB,

CAN, 2 × PWM timers

3 × ADCs, 2 × DACs,

2 × I2S,

2 × USARTs

2 × 16-bit

timers

2 × I2Ss,

1 × I2C,

USB OTG FS,

2 × CANs,

2 × USARTs

2 × 16-bit timers

1 × SPI, 1 × I2C, USB,

CAN,

2 × I2Cs,

USB OTG FS,

2 × CANs,

2 × SPIs,

2 × I2Cs, USB,

CAN,

64 pins

1 × SPI,

1 × I2C,

1 × SDIO, FSMC (100-

and 144-pin packages(2)

1 × PWM timer,

2 × ADCs,

2 × DACs,

)

1 × PWM timer,

2 × ADCs,

2 × DACs

1 × PWM timer

2 × ADCs

USB, CAN,

1 × PWM

timer

1 × PWM timer

2 × ADCs

Ethernet

2 × ADCs

48 pins

36 pins

1. Please refer to Table 5: Pin definitions for peripheral availability when the I/O pins are shared by the peripherals required

by the application.

2. Ports F and G are not available in devices delivered in 100-pin packages.

Doc ID 15274 Rev 4

11/95

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]