STM32F103x8, STM32F103xB

List of figures

List of figures

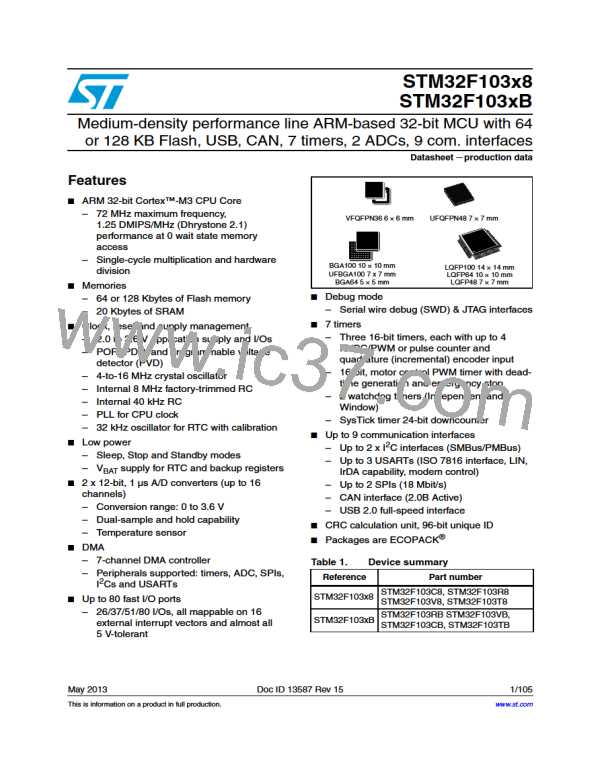

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

STM32F103xx performance line block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Clock tree . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

STM32F103xx performance line LFBGA100 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

STM32F103xx performance line LQFP100 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

STM32F103xx performance line UFBGA100 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

STM32F103xx performance line LQFP64 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

STM32F103xx performance line TFBGA64 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

STM32F103xx performance line LQFP48 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

STM32F103xx performance line UFQFPN48 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 10. STM32F103xx performance line VFQFPN36 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 11. Memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 12. Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 13. Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 14. Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 15. Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 16. Typical current consumption in Run mode versus frequency (at 3.6 V) -

code with data processing running from RAM, peripherals enabled. . . . . . . . . . . . . . . . . . 43

Figure 17. Typical current consumption in Run mode versus frequency (at 3.6 V) -

code with data processing running from RAM, peripherals disabled . . . . . . . . . . . . . . . . . 43

Figure 18. Typical current consumption on V

with RTC on versus temperature at different

BAT

V

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

BAT

Figure 19. Typical current consumption in Stop mode with regulator in Run mode versus

temperature at V = 3.3 V and 3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

DD

Figure 20. Typical current consumption in Stop mode with regulator in Low-power mode versus

temperature at V = 3.3 V and 3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

DD

Figure 21. Typical current consumption in Standby mode versus temperature at

V

= 3.3 V and 3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

DD

Figure 22. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 23. Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 24. Typical application with an 8 MHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 25. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 26. Standard I/O input characteristics - CMOS port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 27. Standard I/O input characteristics - TTL port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 28. 5 V tolerant I/O input characteristics - CMOS port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 29. 5 V tolerant I/O input characteristics - TTL port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 30. I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 31. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2

Figure 32. I C bus AC waveforms and measurement circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 33. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

(1)

Figure 34. SPI timing diagram - slave mode and CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

(1)

Figure 35. SPI timing diagram - master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 36. USB timings: definition of data signal rise and fall time . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 37. ADC accuracy characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 38. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 39. Power supply and reference decoupling (V

Figure 40. Power supply and reference decoupling (V

Figure 41. VFQFPN36 6 x 6 mm, 0.5 mm pitch, package outline

not connected to V

). . . . . . . . . . . . . . 79

). . . . . . . . . . . . . . . . . 80

REF+

DDA

connected to V

REF+

DDA

(1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

(1)(2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Figure 42. Recommended footprint (dimensions in mm)

Doc ID 13587 Rev 15

7/105

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]